### DESIGN OF AN INVERTER-BASED HIGH GAIN OTA, AND ITS APPLICATION IN DELTA SIGMA MODULATORS AND CLASS-D AMPLIFIERS FOR AUDIO APPLICATIONS

Thesis

### Submitted in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

$\mathbf{b}\mathbf{y}$

### YAJUNATH KALIYATH

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING NATIONAL INSTITUTE OF TECHNOLOGY KARNATAKA SURATHKAL, MANGALORE -575025 August, 2020

### DECLARATION

I hereby *declare* that the Research Thesis entitled DESIGN OF AN INVERTER-BASED HIGH GAIN OTA, AND ITS APPLICATION IN DELTA SIGMA MODULATORS AND CLASS-D AMPLIFIERS FOR AUDIO APPLICA-TIONS which is being submitted to the *National Institute of Technology Karnataka, Surathkal* in partial fulfillment of the requirement for the award of the Degree of *Doctor of Philosophy* in Department of Electronics and Communication Engineering is a *bonafide report of the research work carried out by me*. The material contained in this Research Thesis has not been submitted to any University or Institution for the award of any degree.

YAJUNATH KALIYATH, Reg. No. 121181EC12F02, Dept. of E & C Engg.

Place: NITK-Surathkal. Date: 14/08/2020

### CERTIFICATE

This is to certify that the Research Thesis entitled DESIGN OF AN INVERTER-BASED HIGH GAIN OTA, AND ITS APPLICATION IN DELTA SIGMA MODULATORS AND CLASS-D AMPLIFIERS FOR AUDIO APPLICA-TIONS submitted by YAJUNATH KALIYATH (Reg. No. 121181EC12F02) as the record of the research work carried out by him, is accepted as the *Research The*sis submission in partial fulfillment of the requirements for the award of degree of Doctor of Philosophy.

14/08/2000 for

Dr. Laxminidhi T., Research Guide, Chairman-DRPC, Professor and Head, Dept. of E & C Engg., NITK Surathkal - 575025.

प्राध्यापक एवं विभागाध्यक्ष / PROF & HEAD इी एवं सी विभाग / 3 C Department एन् आई टी के, सुरतक /NITK, Surathkal मगंलूर / MANGALORE - 575 025

### Acknowledgements

Its been an emotional roller coaster filled with joy, loss, compassion, self discovery, anger, disgust, love and satisfaction. And finally this journey has come to an end and during this long journey, I have made many friends and encountered numerous situations which taught me valuable life lessons. I would like to thank all the people who were part of this journey and helped me in one way or the other.

First and foremost, I would like to express my sincere and profound gratitude to my research supervisor and HOD, Prof. Laxminidhi. T., for giving me the opportunity to do research under him. His immense knowledge about circuits has inspired me. I am extremely grateful for his constant support and guidance throughout the research. I express my heart felt thanks for bringing out the thesis in its present form. It would have been impossible without his valuable inputs. Words are not enough to express my indebtedness to him for all the support and help.

I would like to thank the RPAC members, Prof. Gangadharan K V, Department of Mechanical Engineering and Dr. M.R Arulalan, Department of Electronics and Communication Engineering, for their valuable suggestions during the progess seminars.

I am thankful to all the previous Head of the Department of Electronics and Communication Engineering (Prof. M. Kulkarni, Prof. M.S Bhat and Prof. U. Shripathi Acharya) for providing a good working environment and all the necessary facilities required for the research work.

I would also like to thank MeitY, Government of India, for providing the EDA tool through SMDP-VLSI project.

Special thanks to all my friends and colleagues from across the departments especially from Mega Tower-II hostel for making my stay at NITK a pleasant and a memorable one that i will cherish for the rest of my life. I would like to express my profound gratitude to my dear brother, Ranjan Kumar Mahapatra, for changing my perspective on life and society. Special thanks to Mrs. Kalpana G. Bhat, Mrs. Chandrika B. K., Mr. Jagadeesh D. N. for all the help and moral support. I would also thank my 6 pm sneak-out buddy, K. S. Babu for never saying 'No'. Special thanks to Kiran Lad, Sreenivasulu, Hanumanthu, Jayaram and Vasudev for all the technical help and for sharing their knowledge. I would also thank MANS, Prasad and Goutham for all their help and support. I also thank Mr. Muhammed and Mr. K Prakash, support staff at Sports Complex, for being kind and generous towards me. I would also thank all the members of ECE RPL cricket teams that I have been part of, for creating such wonderful memories.

I extend my sincere thanks to all the teaching and non-teaching staff members of the Department of Electronics and Communication Engineering for helping me. Special thanks to Prof. M. S. Bhat, Dr. Ramesh Kini M. and Dr. Pathipati Srihari for all the help and support during the tough times. I am thankful to Mr. Sanjeeva pujari, Mr. Subrahmanya Karanth, Mrs. V Prabha and Mrs. Sowmya for all help and support. I am very grateful to Mr. Gurutilak S for maintaining cadence servers in VLSI lab. Special thanks to Mr. Ratish for arranging snacks for all my presentations.

And finally, I am extremely grateful to mom, dad and sister for all their love, care, criticism, prayers, and sacrifices. There is no me without them. I also express my sincere thanks to my cousin for all the love and support. The acknowledgment will remain incomplete if I don't mention the unconditional love that I received everyday from my beloved pet Appy.

It is also my profound duty to thank the almighty for his grace, without which I would not have come this far.

Yajunath Kaliyath

Dedicated to my parents

### Abstract

The Semiconductor IC industry is largely driven by the demands of digital IC design. One of the largely adopted practices is to scale down the technology node and operate on lower supply voltages. This led to faster devices with lower dynamic power consumption. The digital design has hugely benefitted from this. However, there are a large family of analog circuits which suffer performance degradation when operated on low supply voltages. Therefore, for such applications, it is common to operate analog designs on higher supply voltages i.e. in excess of 1 V. In addition, portable, battery powered electronic applications such as digital microphones, image sensors, data acquisition systems, hearing aids, etc., demand low power consumption to save on battery energy. Almost all analog designs have Operational Tranconductance Amplifier (OTA) as one of the integral blocks for realizing various functionalities. OTAs offering sufficiently high dc gain (as per the requirements of application) with lower power consumption will help in realizing the objective of low-power design.

This research is an outcome of the efforts towards proposing an architecture for realizing an inverter-based OTA for switched capacitor based applications and prove its candidature in a couple of applications. The proposed OTA can achieve dc gain in excess of 100 dB and it can be made stable without the need for any explicit compensation scheme. A complete analysis of the OTA along with the design procedure has been presented.

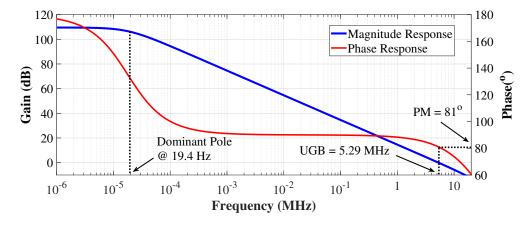

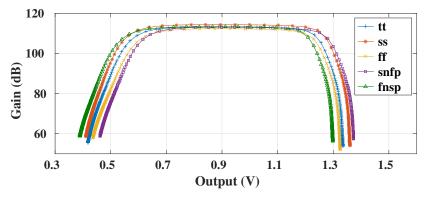

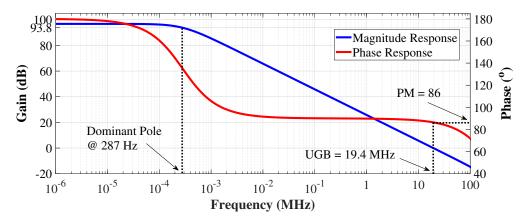

The proposed OTA has been designed in 1P6M UMC 180 nm standard CMOS process technology from UMC Technologies. The power supply for operation has been chosen to be 1.8 V. Two OTAs have been presented, one for biomedical applications and the other for audio applications. The OTA designed for biomedical applications offers a dc gain of 109.3 dB and a unity gain bandwidth (UGB) of 5.29 MHz at 81° phase margin with a capacitive load of 2.5 pF for a typical process corner at room temperature (27°C). The quiescent current consumption of the OTA is 4.79  $\mu$ A, resulting in a power consumption of 8.62  $\mu$ W. The second OTA for audio applications offers a dc gain of 96.8 dB and a UGB of 19.4 MHz at 86°

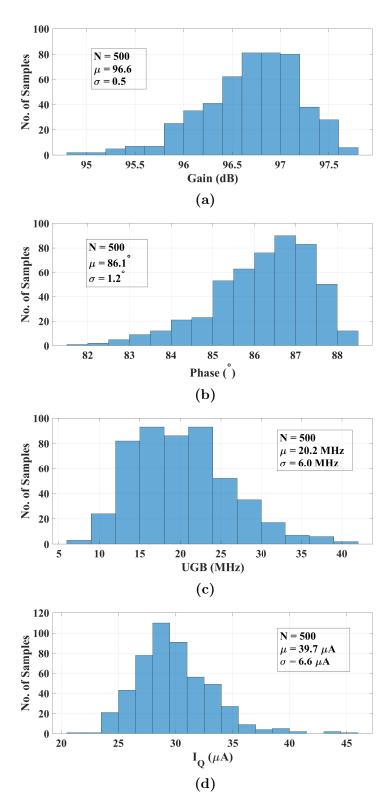

phase margin with a capacitive load of 5 pF for a typical process corner at room temperature. This design draws a quiescent current ( $I_Q$ ) of 38.4  $\mu$ A. The proposed OTA has been proved to be robust though Monte-Carlo simulations. It is also proved to be one among the best designs found in the literature, from the Figure-of-Merit commonly used for evaluating OTAs.

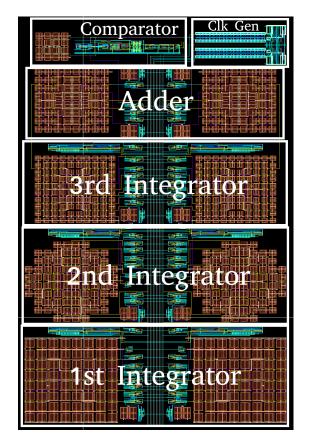

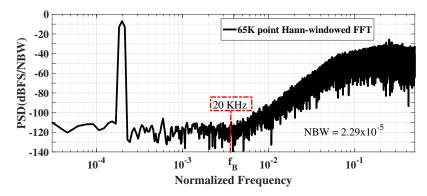

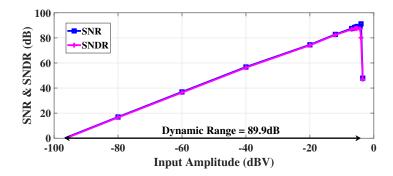

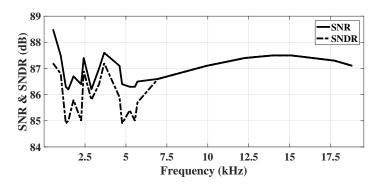

To validate the worthiness of the proposed OTA, a 1-bit third order discrete time Delta Sigma Modulator has been designed for audio applications using the proposed inverter-based OTA. The three integrators of the feed-forward modulator use the proposed OTA as their main block. The classical modulator, without the use of any dedicated improvement scheme, achieves a peak SNR of 91.2 dB and peak SNDR of 87.7 dB with a dynamic range of 89.9 dB. The modulator consumes 570.6  $\mu$ W operating on 1.8 V supply. The Figure-of-Merit proves that the modulator is a fitting candidate among similar modulators found in the literature.

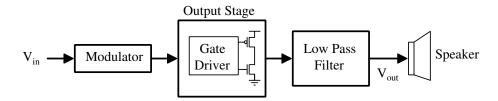

Extending further, a Class D audio amplifier has been designed. The class-D amplifier is targeted for  $8\Omega$  speaker load. The on-chip amplifier adopts the delta-sigma-modulation scheme for achieving audio-grade performance. The power-stage has been designed to have 97.5% efficiency. The class-D amplifier, without any additional scheme for improving the performance, offered a dynamic range of 89.7 dB along with a best THD+N of -85.8,dB for  $8\Omega$  speaker load delivering a maximum power of 100 mW while operating on 1.8 V supply. The efficiency of the amplifier is 92.3% at the peak output power. The amplifier is found to be one of the best in its class.

**Keywords:** Inverter-based OTA, high gain, cascoding, gain-boosting, switched capacitor integrator, delta sigma modulator, feed-forward topology, audio applications, class D amplifier.

## Contents

| 1        | INT | FROD  | UCTION                                                                         |                                                        | 1  |  |  |

|----------|-----|-------|--------------------------------------------------------------------------------|--------------------------------------------------------|----|--|--|

|          | 1.1 | MOT   | IVATION                                                                        |                                                        | 1  |  |  |

|          | 1.2 | CON   | FRIBUTIO                                                                       | DNS                                                    | 8  |  |  |

|          | 1.3 | PRIO  | R WORK                                                                         |                                                        | 9  |  |  |

|          | 1.4 | ORGA  | ANIZATIO                                                                       | ON OF THESIS                                           | 15 |  |  |

| <b>2</b> | INV | VERTI | ER-BASE                                                                        | ED OTA AND ITS DESIGN ANALYSIS                         | 17 |  |  |

|          | 2.1 | CMO   | S INVERI                                                                       | TER AS AN OTA                                          | 17 |  |  |

|          | 2.2 | PROF  | POSED O                                                                        | ΓΑ                                                     | 21 |  |  |

|          |     | 2.2.1 | Small Sig                                                                      | gnal Analysis                                          | 22 |  |  |

|          |     | 2.2.2 | Stability                                                                      | Analysis:                                              | 24 |  |  |

|          |     |       | 2.2.2.1                                                                        | Output pole $(p_1)$                                    | 25 |  |  |

|          |     |       | 2.2.2.2                                                                        | Pole at node $V_{cn}$ $(p_2)$                          | 25 |  |  |

|          |     |       | 2.2.2.3                                                                        | Pole at node $V_{bn}$ $(p_3)$                          | 26 |  |  |

|          |     |       | 2.2.2.4                                                                        | Pole at node $V_{sn}$ $(p_4)$                          | 27 |  |  |

|          |     | 2.2.3 | Noise Ar                                                                       | nalysis                                                | 27 |  |  |

|          |     |       | 2.2.3.1                                                                        | Noise contribution of main inverter $\ldots$           | 28 |  |  |

|          |     |       | 2.2.3.2                                                                        | Noise contribution of cascode transistors and gain-    |    |  |  |

|          |     |       |                                                                                | boosting transistors                                   | 28 |  |  |

|          |     |       | 2.2.3.3                                                                        | Noise contribution of source follower stage $\ldots$ . | 29 |  |  |

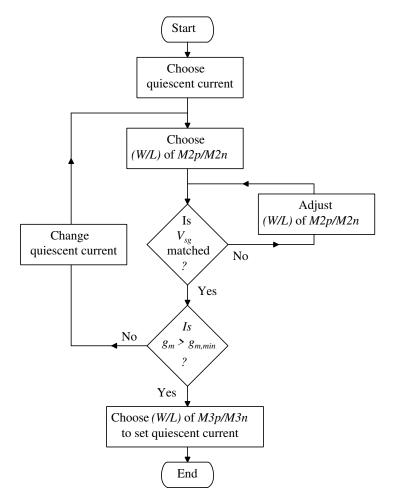

|          | 2.3 | DESI  | GN STEP                                                                        | S FOR A GIVEN APPLICATION                              | 29 |  |  |

|          | 2.4 | SWIT  | CHED CA                                                                        | APACITOR INTEGRATOR USING IGB-OTA                      | 33 |  |  |

|          |     | 2.4.1 | Operatio                                                                       | n of SC Integrator                                     | 34 |  |  |

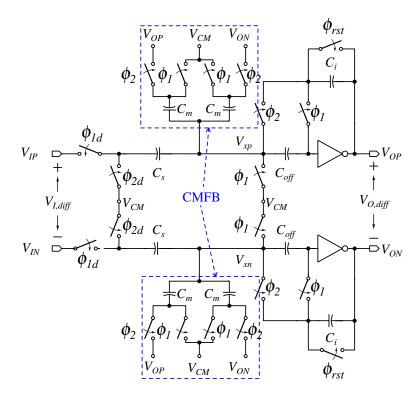

|          |     | 2.4.2 | 2.4.2 Pseudo-differential Switched Capacitor Integrator $\ldots \ldots \ldots$ |                                                        |    |  |  |

|          |     |       | 2.4.2.1                                                                        | Operation of CMFB Circuit                              | 36 |  |  |

| 3 | DE  | SIGN  | OF PROPOSED IGB-OTA FOR BIOMEDICAL AND                                | )  |

|---|-----|-------|-----------------------------------------------------------------------|----|

|   | AU  | DIO A | APPLICATIONS                                                          | 41 |

|   | 3.1 | IGB-0 | OTA DESIGN-I (FOR BIOMEDICAL APPLICATIONS)                            | 42 |

|   |     | 3.1.1 | Performance of IGB-OTA Design-I                                       | 44 |

|   |     | 3.1.2 | Monte Carlo Analysis                                                  | 47 |

|   | 3.2 | IGB-0 | OTA DESIGN-II (FOR AUDIO APPLICATIONS)                                | 50 |

|   |     | 3.2.1 | Performance of IGB-OTA Design-II                                      | 51 |

|   |     | 3.2.2 | Monte Carlo Analysis                                                  | 56 |

|   | 3.3 | COM   | PARISON WITH OTHER WORKS                                              | 58 |

| 4 | ΑI  | DISCR | ETE-TIME DELTA SIGMA MODULATOR FOR AUDIO                              | )  |

|   | AP  | PLICA | ATIONS                                                                | 61 |

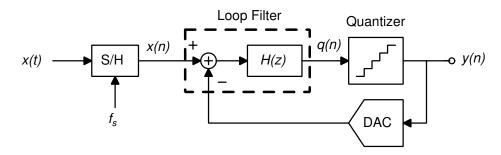

|   | 4.1 | FUNI  | DAMENTALS OF DELTA SIGMA MODULATORS                                   | 61 |

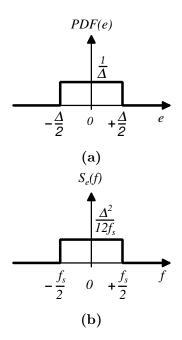

|   |     | 4.1.1 | Quantization Noise                                                    | 62 |

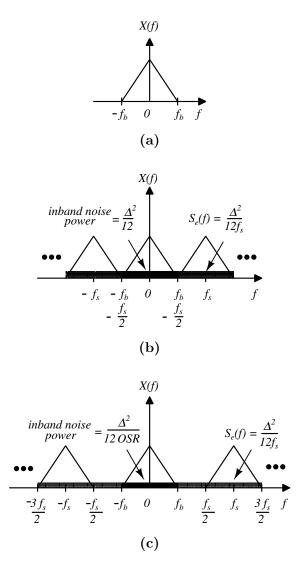

|   |     | 4.1.2 | Oversampling                                                          | 63 |

|   |     | 4.1.3 | Noise shaping technique                                               | 65 |

|   |     | 4.1.4 | Domain of Implementation                                              | 70 |

|   |     | 4.1.5 | Filter Topologies                                                     | 70 |

|   |     | 4.1.6 | Performance metrics                                                   | 72 |

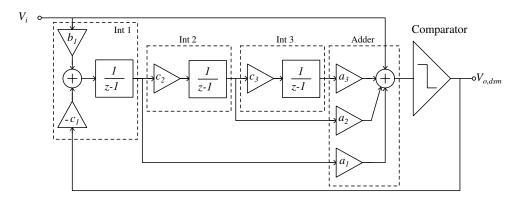

|   | 4.2 | DESI  | GN OF DSM USING THE PROPOSED IGB-OTA                                  | 73 |

|   | 4.3 | MOD   | ULATOR IMPLEMENTATION                                                 | 75 |

|   |     | 4.3.1 | First integrator block $(Int 1) \ldots \ldots \ldots \ldots \ldots$   | 75 |

|   |     | 4.3.2 | Second and third integrator blocks $(Int 2 \text{ and } Int 3) \dots$ | 76 |

|   |     | 4.3.3 | Adder block                                                           | 76 |

|   |     | 4.3.4 | Non-overlap clock generation                                          | 77 |

|   |     | 4.3.5 | Switch Implementations                                                | 77 |

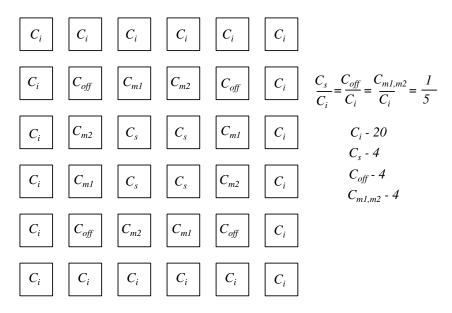

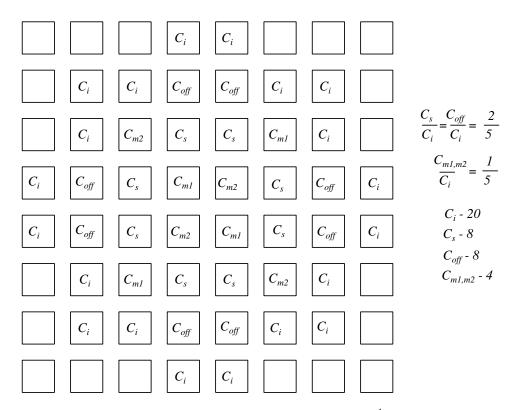

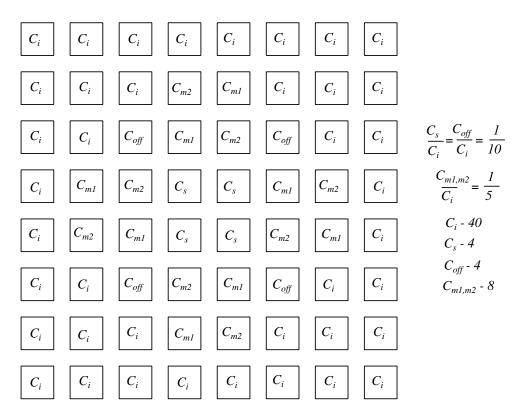

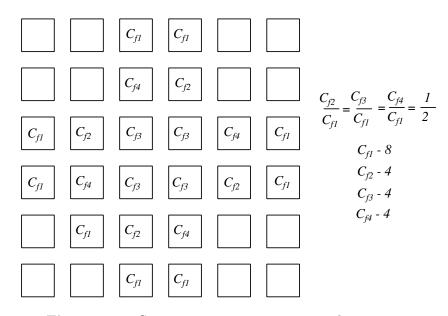

|   |     | 4.3.6 | Capacitor Ratio implementation                                        | 80 |

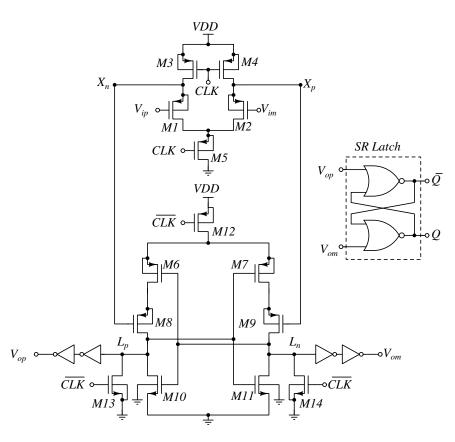

|   |     | 4.3.7 | Quantizer Design                                                      | 83 |

|   |     |       | 4.3.7.1 Operation of Comparator                                       | 84 |

|   | 4.4 | SIMU  | LATION RESULTS                                                        | 86 |

|   | 4.5 | PERF  | FORMANCE SUMMARY                                                      | 89 |

|   | 4.6 | COM   | PARISON WITH OTHER WORKS                                              | 90 |

| <b>5</b>     | ON    | -CHIP CLASS D AMPLIFIER                                       | 93  |

|--------------|-------|---------------------------------------------------------------|-----|

|              | 5.1   | INTRODUCTION                                                  | 93  |

|              |       | 5.1.1 Basic operation of class D amplifier                    | 94  |

|              |       | 5.1.2 Performance metrics                                     | 97  |

|              | 5.2   | DTDSM BASED CLASS D AMPLIFIER USING THE PROPOSED              |     |

|              |       | IGB-OTA                                                       | 97  |

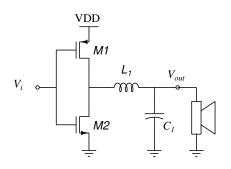

|              |       | 5.2.1 Design of Power Stage                                   | 98  |

|              |       | 5.2.2 Gate Driver Circuit                                     | 100 |

|              | 5.3   | SIMULATION RESULTS                                            | 102 |

|              | 5.4   | COMPARISON WITH OTHER WORKS                                   | 105 |

| 6            | CO    | NCLUSIONS AND FUTURE SCOPE                                    | 107 |

|              | 6.1   | CONCLUSIONS                                                   | 107 |

|              | 6.2   | FUTURE SCOPE                                                  | 108 |

| $\mathbf{A}$ | ppen  | dix I: MATLAB Psuedo Codes and Simulink model                 | 109 |

|              | A-1   | MATLAB psuedo code: Generating the filter coefficients of DSM | 109 |

|              | A-2   | Simulink Model of DSM                                         | 111 |

|              | A-3   | MATLAB psuedo code: Computing the performance metrics (from a |     |

|              |       | time domain signal)                                           | 112 |

|              | A-4   | MATLAB psuedo code: Plotting the output PSD of DSM/CDA using  |     |

|              |       | DSM Toolbox                                                   | 114 |

| Bi           | bliog | graphy                                                        | 115 |

| P            | ıblic | ations based on the thesis                                    | 123 |

# List of Figures

| 1.1  | Generic analog signal processing system (Pavan et al. 2017)                                                    | 2  |

|------|----------------------------------------------------------------------------------------------------------------|----|

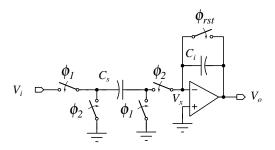

| 1.2  | Switched Capacitor Integrator circuit (Bourdopoulos et al. 2003)                                               | 4  |

| 1.3  | Equivalent circuit of SC Integrator during (a) $\phi_1$ phase (b) $\phi_2$ phase                               | 4  |

| 2.1  | CMOS inverter(a) Schematic circuit (b) VTC                                                                     | 18 |

| 2.2  | Schematic circuit of cascoded inverter (Luo et al. 2013b) $\ldots$ .                                           | 18 |

| 2.3  | Schematic of an inverter with gain-boosting (Luo et al. 2013b) $\ .$                                           | 19 |

| 2.4  | Schematic of the proposed IGB-OTA                                                                              | 21 |

| 2.5  | Incremental Circuit of proposed IGB-OTA                                                                        | 22 |

| 2.6  | Incremental Circuit of lower half of the proposed IGB-OTA                                                      | 24 |

| 2.7  | Flowchart for sizing the source follower circuit                                                               | 32 |

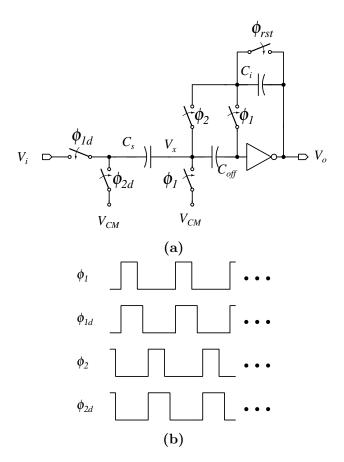

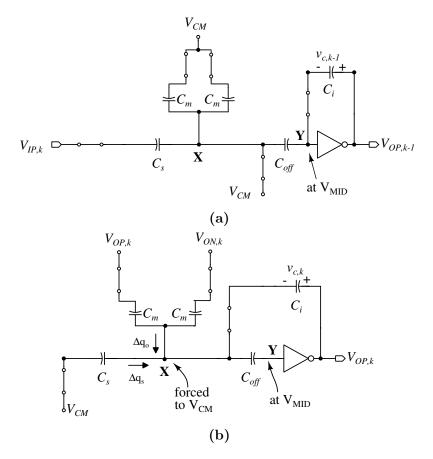

| 2.8  | (a) A parasitic insensitive single-ended SC integrator (Luo et al. 2013b) $$                                   |    |

|      | and its (b) Clock phases $\ldots \ldots \ldots$ | 34 |

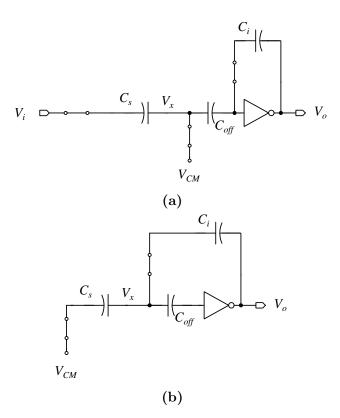

| 2.9  | (a) $\phi_1$ phase (b) $\phi_2$ phase of integrator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$         | 35 |

| 2.10 | A parasitic insensitive pseudo-differential SC integrator (Luo et al. 2013b)                                   | 36 |

| 2.11 | Equivalent half-circuit of the differential integrator during (a) $\phi_1$ phase                               |    |

|      | (b) $\phi_2$ phase                                                                                             | 37 |

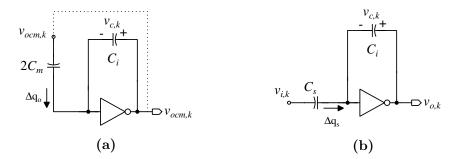

| 2.12 | Simplified small-signal equivalent half-circuit of the differential inte-                                      |    |

|      | grator during $\phi_2$ phase for (a) common-mode (b) differential-mode .                                       | 38 |

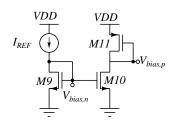

| 3.1  | Biasing Circuit for IGB-OTA Design-I                                                                           | 43 |

| 3.2  | Layout of the proposed IGB-OTA for Design-I                                                                    | 43 |

| 3.3  | Frequency response of the proposed IGB-OTA Design-I for a typical                                              |    |

|      | process corner, supply voltage and temperature                                                                 | 44 |

| 3.4  | Gain vs Output voltage of IGB-OTA Design-I                                                                     | 46 |

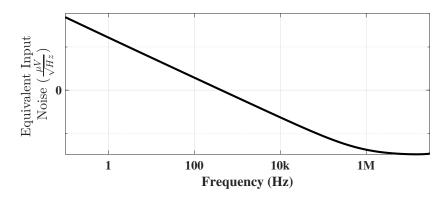

| 3.5  | Equivalent input referred noise spectrum of IGB-OTA Design-I                                                   | 47 |

| 3.6  | Distribution of a) DC Gain b) PM c) UGB d) Quiescent Current $(I_Q)$              |    |

|------|-----------------------------------------------------------------------------------|----|

|      | for OTA Design-I                                                                  | 48 |

| 3.7  | Biasing Circuit for IGB-OTA Design-II                                             | 51 |

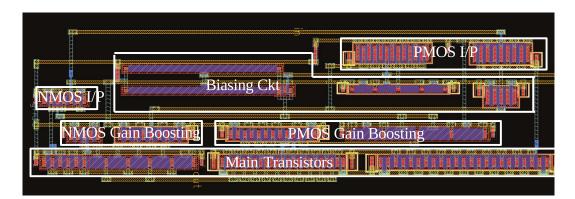

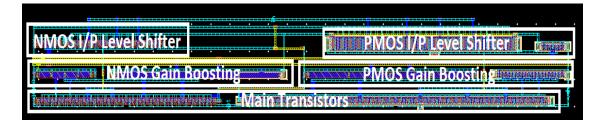

| 3.8  | Layout of the proposed IGB-OTA for Design-II                                      | 51 |

| 3.9  | Frequency response of the proposed IGB-OTA Design-II for typical                  |    |

|      | process at nominal supply and temperature                                         | 52 |

| 3.10 | (a) Magnitude and (b) Phase response of IGB-OTA Design-II for $s\bar{s}$          |    |

|      | corner with and without tuning $I_{REF}$                                          | 53 |

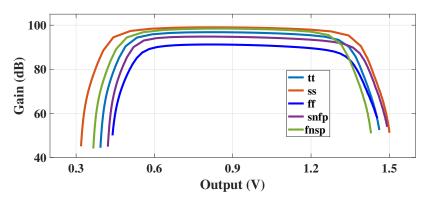

| 3.11 | Gain vs output swing of IGB-OTA Design-II                                         | 55 |

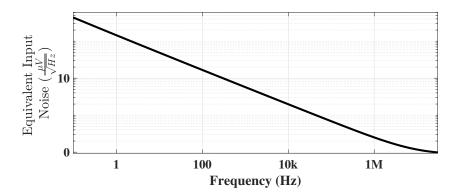

| 3.12 | Equivalent input referred noise spectrum of IGB-OTA Design-II $\ . \ . \ .$       | 55 |

| 3.13 | Distribution of a) DC Gain b) PM c) UGB d) Quiescent Current $(I_Q)$              |    |

|      | for OTA Design-II                                                                 | 57 |

| 4.1  | Generic architecture of a DSM (José and Del Río 2013)                             | 62 |

| 4.2  | Ideal linear model of a DSM (José and Del Río 2013)                               | 62 |

| 4.3  | (a) PDF and (b) PSD of Quantization noise (José and Del Río 2013)                 | 63 |

| 4.4  | Fourier Transform of (a) input signal $x(t)$ (b) $x(t)$ when sampled at           |    |

|      | nyquist frequency (c) $x(t)$ when sampled at a frequency higher than              |    |

|      | nyquist frequency (José and Del Río 2013)                                         | 64 |

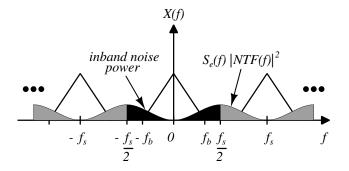

| 4.5  | Quantization Noise shaping in a DSM (José and Del Río 2013)                       | 66 |

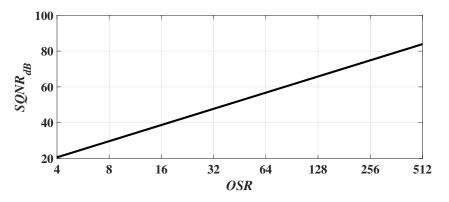

| 4.6  | $SQNR$ of a first order DSM as a function of OSR $\ldots$                         | 67 |

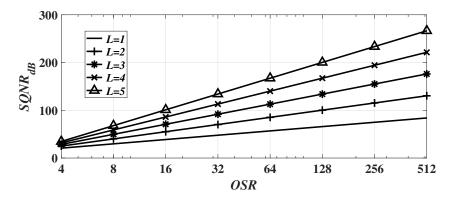

| 4.7  | $SQNR$ of a $L^{th}$ order DSM with a 1-bit quantizer                             | 68 |

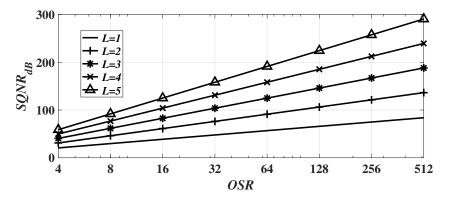

| 4.8  | $SQNR$ of a $L^{th}$ order DSM with a 2-bit quantizer                             | 68 |

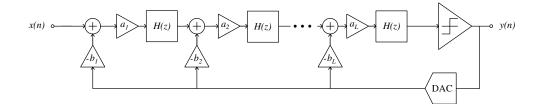

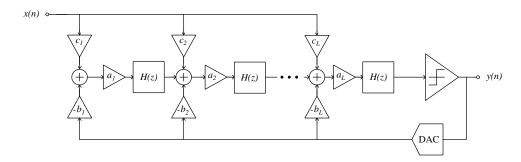

| 4.9  | Distributed feedback topology for higher order DSM (Schreier et al.               |    |

|      | 2005)                                                                             | 70 |

| 4.10 | Distributed feedback topology for higher order DSM with input cou-                |    |

|      | pling (Schreier et al. 2005)                                                      | 71 |

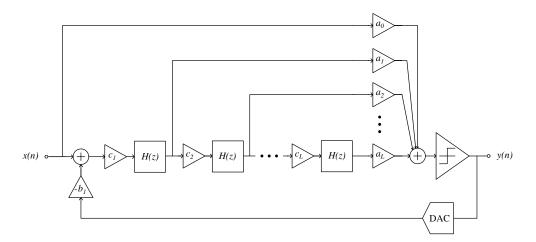

| 4.11 | Distributed feed-forward topology for higher order DSM (Schreier et al.           |    |

|      | 2005)                                                                             | 71 |

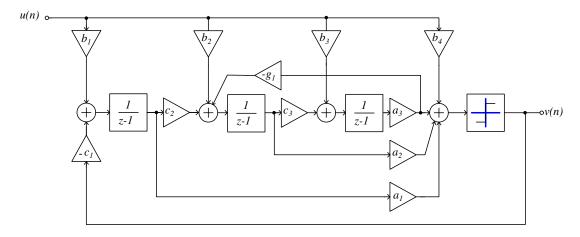

| 4.12 | Block diagram of $3^{rd}$ order feed-forward $\Delta\Sigma$ modulator             | 74 |

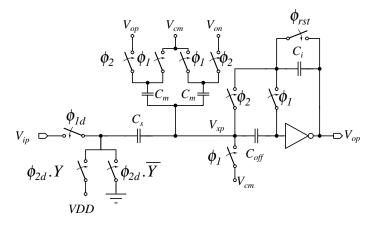

| 4.13 | Schematic circuit of single-ended first integrator $(Int 1) \ldots \ldots$        | 75 |

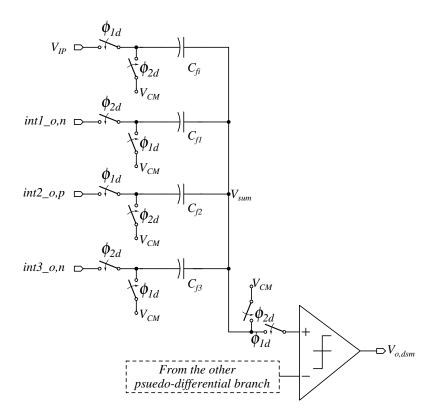

| 4.14 | Schematic circuit of single-ended adder stage                                     | 76 |

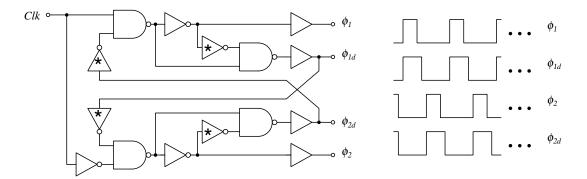

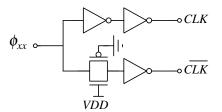

| 4.15 | Clock generation circuit (Pavan et al. 2017) $\ldots \ldots \ldots \ldots \ldots$ | 78 |

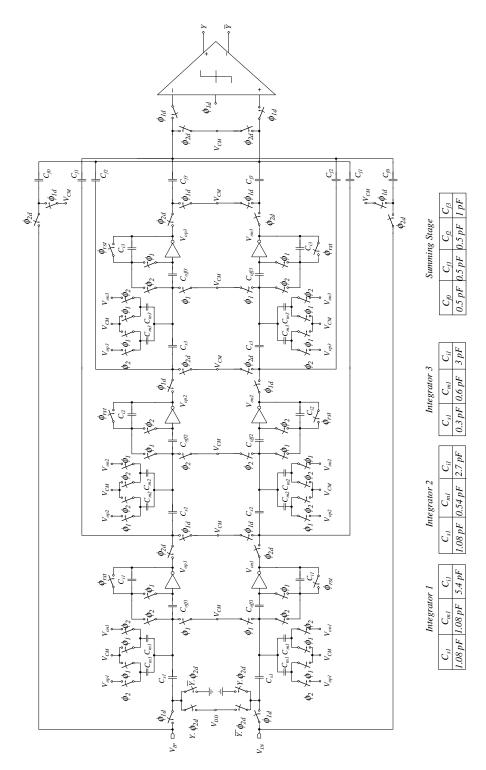

| 4.16 | Complete schematic circuit of pseudo differential DSM                             | 79 |

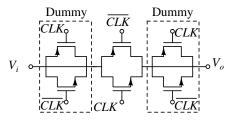

| 4.17 | Switch with two dummies (Pavan et al. 2017)                                             | 80       |

|------|-----------------------------------------------------------------------------------------|----------|

| 4.18 | Complementary clock generation (Pavan et al. 2017) $\ldots \ldots \ldots$               | 80       |

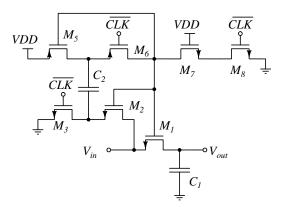

| 4.19 | Boot-strapped Switch (Razavi 2015)                                                      | 80       |

| 4.20 | Layout scheme of capacitors in $1^{st}$ integrator $\ldots \ldots \ldots \ldots \ldots$ | 81       |

| 4.21 | Layout scheme of capacitors in $2^{nd}$ integrator                                      | 81       |

| 4.22 | Layout scheme of capacitors in $3^{rd}$ integrator                                      | 82       |

| 4.23 | Summing stage capacitance implementation                                                | 82       |

| 4.24 | Low Power Dynamic Comparator (Van Elzakker et al. 2010) $\ldots$                        | 83       |

| 4.25 | Internal nodes of the Comparator during the reset and comparison phase                  | 85       |

| 4.26 | Layout of pseudo differential DSM                                                       | 86       |

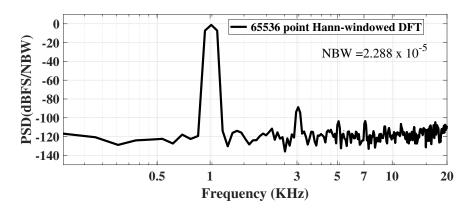

| 4.27 | PSD of DSM output                                                                       | 87       |

| 4.28 | SNR & SNDR of DSM output versus the input amplitude $\ .$                               | 88       |

| 4.29 | SNR & SNDR of DSM output versus the input signal frequency $\ . \ .$                    | 88       |

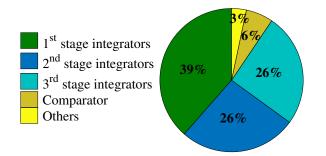

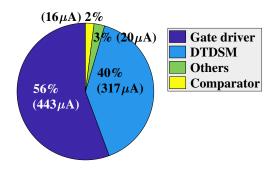

| 4.30 | Power breakdown of DSM                                                                  | 89       |

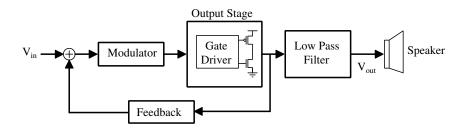

| 5.1  | Open loop Class D amplifier (Gaalaas 2006)                                              | 95       |

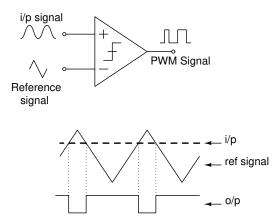

| 5.2  | Pulse Width Modulator of a Class D power amplifier (Cordell 2011).                      | 95<br>95 |

| 5.3  | Half bridge configured output switching stage (Cordell 2011)                            | 96       |

| 5.4  | Schematic of a feedback CDA (Yu et al. 2009)                                            | 96       |

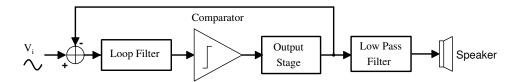

| 5.5  | DSM based CDA (Cordell 2011)                                                            | 96       |

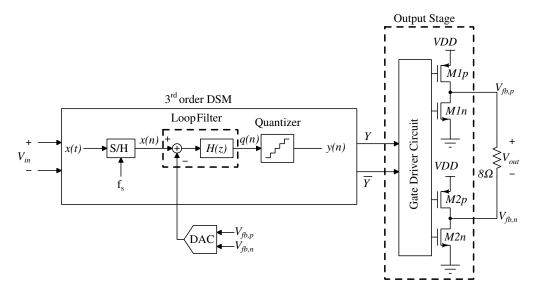

| 5.6  | $\Delta\Sigma$ modulator based CDA                                                      | 98       |

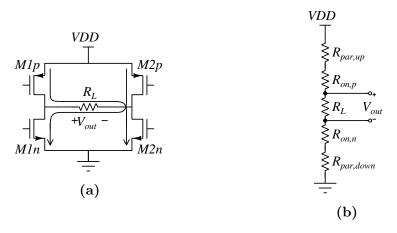

| 5.7  | H-brige power stage (a) Schematic (Cordell 2011)(b) Equivalent circuit.                 | 99       |

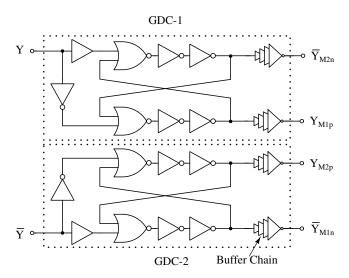

| 5.8  |                                                                                         | 101      |

| 5.9  |                                                                                         | 102      |

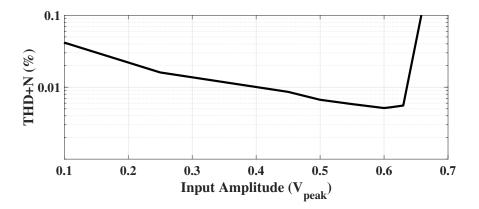

| 5.10 |                                                                                         | 103      |

| 5.11 | 1                                                                                       | 103      |

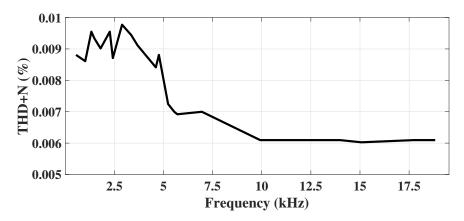

|      |                                                                                         | 103      |

|      |                                                                                         | 104      |

|      |                                                                                         |          |

| A.1  |                                                                                         | 110      |

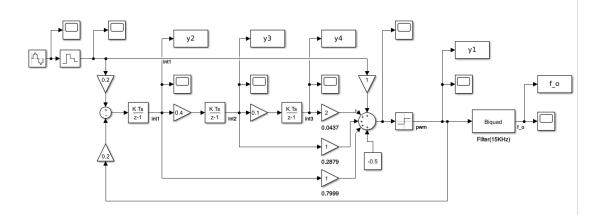

| A.2  | Simulink model of DSM                                                                   | 111      |

## List of Tables

| 1.1  | Summary of OTA's dc gain in discrete-time based applications                           | $\overline{7}$ |

|------|----------------------------------------------------------------------------------------|----------------|

| 1.2  | Performance summary of 2-stage OTAs found in literature                                | 11             |

| 1.3  | Performance summary of inverter-based OTAs found in literature                         | 14             |

| 3.1  | Aspect ratio of transistors for IGB-OTA Design-1                                       | 42             |

| 3.2  | Post-layout performance of the IGB-OTA Design-I across process corners $% \mathcal{A}$ | 44             |

| 3.3  | Post-Layout performance of the IGB-OTA design-I at different supply                    |                |

|      | voltages                                                                               | 45             |

| 3.4  | Post-Layout performance at different temperatures                                      | 45             |

| 3.5  | Post-Layout performance of IGB-OTA Design-I for variations in $V_{CM}$                 | 46             |

| 3.6  | Performance summary of IGB-OTA Design-I                                                | 49             |

| 3.7  | Aspect ratio of transistors for IGB-OTA Design-II                                      | 50             |

| 3.8  | Post-Layout performance of IGB-OTA Design-II across process corners                    | 52             |

| 3.9  | Post-Layout performance of IGB-OTA Design-II for supply voltage                        |                |

|      | changes                                                                                | 54             |

| 3.10 | Post-Layout performance of IGB-OTA Design-II at different tempera-                     |                |

|      | tures                                                                                  | 54             |

| 3.11 | Performance summary of IGB-OTA Design-II                                               | 56             |

| 3.12 | Comparison of proposed OTA with OTA's operating on $1.8\mathrm{V}$ $~$                 | 58             |

| 3.13 | Comparison of proposed OTA with OTA's operating on lower supply                        |                |

|      | voltage                                                                                | 59             |

| 4.1  | Comparison of Discrete-time vs Continuous-time DSMs (Cherry and                        |                |

|      | Snelgrove 1999, Schreier et al. 2005, José and Del Río<br>2013) $\ \ldots$ .           | 69             |

| 4.2  | Loop filter coefficients of DSM                                                        | 74             |

| 4.3  | Aspect ratio of transistors of the comparator                                          | 85             |

| 4.4 | Summary of DSM's performance                      | 89  |

|-----|---------------------------------------------------|-----|

| 4.5 | Comparison with other works                       | 90  |

| 5.1 | Desired specifications for the CDA                | 98  |

| 5.2 | Aspect ratio of power transistors of output stage | 100 |

| 5.3 | Sizing of inverter buffer chain                   | 101 |

| 5.4 | Summary of CDA's performance                      | 104 |

| 5.5 | Comparison with other works                       | 105 |

## Abbreviations

| CDA                                     | Class D Amplifier                              |  |  |

|-----------------------------------------|------------------------------------------------|--|--|

| CMOS                                    | Complementary Metal Oxide Semiconductor        |  |  |

| DC                                      | Direct Current                                 |  |  |

| DR                                      | Dynamic Range                                  |  |  |

| $\mathbf{DSM}$                          | Delta Sigma Modulator                          |  |  |

| DTDSM                                   | Discrete - Time Delta Sigma Modulator          |  |  |

| $\mathbf{DFT}$                          | Discrete Fourier Transform                     |  |  |

| FoM                                     | Figure of Merit                                |  |  |

| IC                                      | Integrated Circuit                             |  |  |

| IGB-OTA                                 | Inveter-based Gain-Boosted Operational         |  |  |

|                                         | Transconductance Amplifier                     |  |  |

| NMOS                                    | N-channel Metal Oxide Semiconductor            |  |  |

| NTF                                     | Noise Transfer Function                        |  |  |

| NBW                                     | Noise Bandwidth                                |  |  |

| $\mathbf{OSR}$                          | Over Sampling Ratio                            |  |  |

| OTA                                     | Operational Transconductance Amplifier         |  |  |

| $\mathbf{PM}$                           | Phase Margin                                   |  |  |

| PMOS                                    | P-channel Metal Oxide Semiconductor            |  |  |

| $\mathbf{PVT}$                          | Process, supply Voltage and Temperature        |  |  |

| $\mathbf{SoC}$                          | System on Chip                                 |  |  |

| $\mathbf{SC}$                           | Switched Capacitor                             |  |  |

| $\mathbf{SFDR}$                         | Spurious Free Dynamic Range                    |  |  |

| SNDR                                    | Signal to Noise and Distortion Ratio           |  |  |

| <b>SNR</b> Signal to Noise Ratio        |                                                |  |  |

| SQNR Signal to Quantization Noise Ratio |                                                |  |  |

| THD+N                                   | Total Harmonic and Distortion plus Noise Ratio |  |  |

| UGB                                     | Unity Gain Bandwidth in radians per second     |  |  |

| $\mathbf{UMC}$                          | United Microelectronics Corporation            |  |  |

|                                         |                                                |  |  |

## Notations

| $C_{ox}$  | Gate-oxide capacitance                  |

|-----------|-----------------------------------------|

| $f_b$     | Signal bandwidth in Hz                  |

| $f_{clk}$ | Clock frequency in Hz                   |

| $f_{in}$  | input Signal frequency in Hz            |

| $f_N$     | Nyquist frequency in Hz                 |

| $f_s$     | Sampling frequency in Hz                |

| 1/f       | Flicker noise                           |

| $g_m$     | Gate transconductance in Siemens        |

| $g_o$     | Output conductance of MOSFET in Siemens |

| $g_{mb}$  | Bulk-transconductance in Siemens        |

| k         | Boltzmann Constant                      |

| L         | Channel length of the MOSFET            |

| $\eta$    | Sub-threshold slope factor              |

| q         | Electronic charge                       |

| S(f)      | Power Spectral Density                  |

| T         | Absolute temperature                    |

| $\mu$     | Carrier mobility                        |

| $V_{TH}$  | Threshold voltage                       |

| $V_T$     | Thermal voltage                         |

| $V_{GS}$  | Gate-source voltage of the MOSFET       |

| $V_{DS}$  | Drain-source voltage of the MOSFET      |

| $V_{BS}$  | Bulk-source voltage of the MOSFET       |

| ω         | Angular frequency in radians per second |

| $\gamma$  | Noise co-efficient                      |

| W         | Channel width of the MOSFET             |

.

### Chapter 1

## INTRODUCTION

### 1.1 MOTIVATION

The invention of transistor was a giant leap forward for the field of electronics. Smaller size, higher reliability and the requirement of only milli watts of power to operate, made the world to move from the conventional vacuum tube based systems to transistor based ones. With the invention IC's in the subsequent years, the world witnessed a drastic change in the landscape of electronics industry. The entire electronic circuit got integrated on a single chip which resulted in electronic devices that are lighter, smaller and cheaper. Since then, the field of electronics has advanced in productivity and performance at a pace unmatched in technological history.

Over the last two decades, the semiconductor IC industry has been rapidly and consistently scaling the CMOS technology and has immensely benefited from it. The scaling of technology is largely driven by the performance gain offered by the digital circuits. It resulted in faster devices with lower dynamic power consumption and allowed integration of more and more functionality per unit area. However, the performance of analog and mixed-signal circuits does not necessarily improve with technology scaling. The major effect of technology scaling, from an analog design perspective, can be listed as follows.

• Supply voltage is scaled down with the technology reducing the voltage headroom available for analog circuits.

- Threshold voltage of Metal-Oxide-Semiconductor (MOS) transistors does not scale consistently with the supply voltage.

- Intrinsic gain of transistor reduces.

- Linearity offered by the transistors reduces.

- Noise increases as the transistor density increases.

- Dynamic range reduces, due to reduced linearity and increased noise.

- Gate leakage current increases.

- The effect of layout parasitics becomes more pronounced.

The above limitations are the impediments for analog and mixed-signal circuits in taking advantage of technology scaling. This has prompted the circuit designers to try implementing as much as analog functions in digital domain. As a result, computational and signal processing tasks are now performed predominantly by digital circuits since they can be realized by extremely small and simple structures that can in turn be combined to obtain very complex, accurate, and fast systems (Pavan et al. 2017). However, we live in an analog world that cannot be accurately represented with purely digital design. Therefore, despite a number of efforts over the years to replace analog with digital circuits, analog still has a solid foothold in chip design. Digitally assisted analog design techniques like digital calibration allowed some of the analog and mixed-signal circuits to be integrated with the digital blocks. However, high performance analog and mixed-signal circuits are essential as they are the interface between the analog signal from/to real world and the digital signal processors.

Figure 1.1: Generic analog signal processing system (Pavan et al. 2017)

Figure 1.1 shows a generic analog signal processing system. The real world analog signal is sensed by an appropriate transducer and it is amplified by pre-amplifier stage

since the sensed real world analog signal is usually weak. Then, a filter stage filters out unwanted signal components and an Analog-to-Digital Converter (ADC) converts it into digital domain, allowing the Digital Signal Processor (DSP) to do the necessary signal processing. Bio-medical applications fall under this front-end category where bio-siganls are sensed by bio-sensors and are converted into digtal domain. To convert the digital signal back to an analog form, a Digital to Analog Converter (DAC) is used followed a filter stage which removes any unwanted signal components that were intentionally/unintentionally added by ADC and DSP. And then, the filtered signal is strengthened by the driver stage in order to drive an appropriate transducer. Audio amplifier is an example for the back-end application where the input audio signal has to amplified to a level suitable for driving the speaker load. These analog signal processing circuits are required to be implemented on a single chip along with the digital circuits. Often, digital circuits are operated on a lower supply voltage, commonly known as core voltage, to take advantage of performance gain with respect to speed and dynamic power loss. And, analog circuits are operated on a higher voltage, typically made available for Input-Output (IO) pads, to take advantage of voltage head-room (Pavan et al. 2017).

The demand for portable consumer electronics such as mobiles, tablets, laptops, wireless speakers, smart wearables etc., has increased quite significantly over the last few years. As these devices are battery powered, the battery life is one of the key factors which decide the commercial success of these products. Unfortunately, the battery technology has not kept up with the energy requirement of the portable electronic devices. Therefore, these applications require circuit designs that are power efficient.

Switched capacitor (SC) circuits are used in the discrete-time implementation of most of the analog and mixed signal integrated circuit (IC) designs such as filters and data converters (Quinn and van Roermund 2007, Razavi 2017). Operational Transconductance Amplifier (OTA) is the fundamental building block of switched capacitor circuits and it accounts for a large fraction of the total power consumed by the IC. Further, the dc gain of an OTA determines the accuracy of charge transfer in the SC circuits and therefore plays a significant role in the overall performance of SC application (Quinn and van Roermund 2007). To demonstrate the significance of OTA's dc gain in SC circuits, consider a SC integrator shown in Figure 1.2.  $V_i$  is the input to the integrator and  $V_o$  is the output of the integrator.  $C_s$  is the sampling capacitor used for sampling the input signal and  $C_i$  is the integrating capacitor that accumulates the charge transferred from  $C_s$  in every clock cycle. Initially capacitor  $C_i$  is reset in  $\phi_{rst}$  phase.  $\phi_1$  is the sampling phase in which input  $V_i$  is sampled onto the sampling capacitor  $C_s$ .  $\phi_2$  is the integration phase during which the total charge on the sampling capacitor  $C_s$  is completely transferred onto the integrating capacitor  $C_i$ , provided that the dc gain of OTA is infinite.

Figure 1.2: Switched Capacitor Integrator circuit (Bourdopoulos et al. 2003)

To study the effect of finite dc gain of the OTA on the integrator, let us consider the gain of OTA to be  $A_0$ . Therefore, node voltage  $V_x$  at the inverting terminal of OTA can be expressed as follows at all times.

$$(0 - V_x)A_0 = V_o (1.1)$$

$$\therefore V_x = -\frac{V_o}{A_0} \tag{1.2}$$

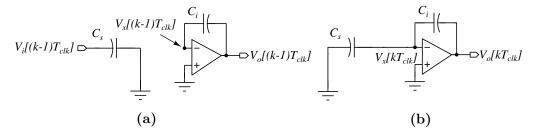

The equivalent circuit of switched capacitor integrator during the two clock phases are shown in Figure 1.3.

**Figure 1.3:** Equivalent circuit of SC Integrator during (a)  $\phi_1$  phase (b)  $\phi_2$  phase

The total charge  $Q_{\phi 1}$  during  $\phi_1$  phase can be expressed as follows

$$Q_{\phi 1} = (0 - V_i[(k-1)T_{clk}]) C_s + (V_x[(k-1)T_{clk}] - V_o[(k-1)T_{clk}]) C_i$$

=  $-V_i[(k-1)T_{clk}]C_s + (V_x[(k-1)T_{clk}] - V_o[(k-1)T_{clk}]) C_i$  (1.3)

Using 1.2 in 1.3, we get

$$Q_{\phi 1} = -V_i[(k-1)T_{clk}]C_s + \left(\frac{-V_o[(k-1)T_{clk}]}{A_0} - V_o[(k-1)T_{clk}]\right)C_i$$

=  $-V_i[(k-1)T_{clk}]C_s - \left(1 + \frac{1}{A_0}\right)V_o[(k-1)T_{clk}]C_i$  (1.4)

And the total charge  $Q_{\phi 2}$  during  $\phi_2$  phase can be expressed as follows

$$Q_{\phi 2} = (V_x[kT_{clk}] - 0) C_s + (V_x[kT_{clk}] - V_o[kT_{clk}]) C_i$$

=  $V_x[kT_{clk}]C_s + (V_x[kT_{clk}] - V_o[kT_{clk}]) C_i$  (1.5)

Using 1.2 in 1.5, we get

$$Q_{\phi 2} = \left(-\frac{V_o[kT_{clk}]}{A_o}\right)C_s + \left(-\frac{V_o[kT_{clk}]}{A_o} - V_o[kT_{clk}]\right)C_i$$

$$= -\frac{V_o[kT_{clk}]}{A_o}C_s - \left(1 + \frac{1}{A_o}\right)V_o[kT_{clk}]C_i$$

(1.6)

Equating the total charge during  $\phi_2$  and  $\phi_1$  (i.e., equating 1.6 and 1.4), we get

$$-\frac{V_o[kT_{clk}]}{A_o}C_s - \left(1 + \frac{1}{A_o}\right)V_o[kT_{clk}]C_i = -V_i[(k-1)T_{clk}]C_s - \left(1 + \frac{1}{A_0}\right)V_o[(k-1)T_{clk}]C_i \quad (1.7)$$

Applying Z-transform on 1.7, we get

$$-\frac{V_o[z]}{A_o}C_s - \left(1 + \frac{1}{A_o}\right)V_o[z]C_i = -z^{-1}V_i[z]C_s - \left(1 + \frac{1}{A_0}\right)z^{-1}V_o[z]C_i \qquad (1.8)$$

Simplifying this, we get

$$\frac{V_o[z]}{V_i[z]} = \frac{C_s}{C_i} \frac{z^{-1}}{\left[\left(\frac{1}{A_0}\right)\frac{C_s}{C_i} + \left(1 + \frac{1}{A_0}\right)(1 - z^{-1})\right]}$$

(1.9)

Further, 1.9 can be expressed as follows (Luo et al. 2013b).

$$\frac{V_o[z]}{V_i[z]} = \frac{C_s}{C_i} \left(\frac{\lambda z^{-1}}{1 - pz^{-1}}\right)$$

(1.10)

$$\lambda = \frac{1}{1 + \left(1 + \frac{C_s}{C_i}\right)\frac{1}{A_0}} \tag{1.11}$$

$$p = \frac{\left(1 + \frac{1}{A_0}\right)}{1 + \left(1 + \frac{C_s}{C_i}\right)\frac{1}{A_0}}$$

(1.12)

where  $(1-\lambda)$  represents the gain error and (1-p) represents the phase error in a SC integrator. When the gain of the OTA,  $A_0$ , is infinite,  $\lambda = p = 1$  and it results in an ideal integrator transfer function as given in 1.13.

$$\frac{V_o[z]}{V_i[z]} = \frac{C_s}{C_i} \left(\frac{z^{-1}}{1-z^{-1}}\right)$$

(1.13)

The gain error and phase error can be approximately expressed as follows.

$$1 - \lambda \approx \left(1 + \frac{C_s}{C_i}\right) \frac{1}{A_0}$$

(1.14)

$$1 - p \approx \frac{C_s}{C_i} \frac{1}{A_0} \tag{1.15}$$

From 1.14 and 1.15, it is evident that gain error and phase error are inversely proportional to  $A_0$  and therefore it is a necessity in SC integrators to have OTA with a high dc gain. A dc gain of 40 dB with  $C_s = C_i$  results in a gain error of 2% and a phase error of 1%. In delta sigma modulators, phase error shifts the zeroes of the noise transfer function and thus affects the stability of the feedback loop. In Pavan et al. (2017), it was suggested that in the design of delta sigma modulators, it is a good practice to have an OTA with dc gain in excess of 80 dB. DC gains of the OTA in some of the high performance discrete-time SC based applications are outlined in Table 1.1.

| Reference             | Application   | OTA Architecture | OTA DC Gain        |

|-----------------------|---------------|------------------|--------------------|

| Kang et al. (2008)    | Audio         | Folded Cascode   | $76\mathrm{dB}$    |

| Kuo et al. (2010)     | Audio         | 2 stage Cascade  | $76\mathrm{dB}$    |

| Luo et al. (2013b)    | Audio         | Inverter-based   | $83\mathrm{dB}$    |

|                       | Wireless      |                  |                    |

| Daoud et al. $(2016)$ | Communication | Telescopic       | $96\mathrm{dB}$    |

|                       | Systems       |                  |                    |

| Hwang et al. $(2017)$ | Audio         | Inverter-based   | $> 85 \mathrm{dB}$ |

Table 1.1: Summary of OTA's dc gain in discrete-time based applications

It is clearly evident from the table that OTAs with high dc gain (> 75 dB) have been used in SC applications and therefore, as suggested in Pavan et al. (2017), it is accepted that OTAs designed for SC application should have dc gain gain in excess of 80 dB.

High gain OTAs are typically realized using one of the following topologies. Cascade of amplifiers, Cascode (telescopic) and Folded Cascode. Cascade of amplifiers are realized by cascading multiple stages of amplifiers (typically two). They are capable of offering high swing at the output upto rail-to-rail. However, it is critical to ensure stability in closed loop operation, owing to the presence of multiple poles. Multiple stages along with the compensation requirements make OTAs power hungry. Cascode architecture is capable of offering gain of the order of that of a cascaded OTA, but with a single stage. Stability requirement is relaxed owing to single stage. However, it seriously fails to offer a large swing at the output. Therefore, this type of OTAs are best suited for applications where the signal swing requirement is small, for example DSM. Folded cascode OTA offers slightly higher swing when compared to Cascode but falls short in stability and power requirement. Cascode/Folded-cascode amplifiers are also cascaded with a common-source amplifier stage to achieve higher swing and dc gain. However, this comes with a penalty of compensation and associated power requirements.

A CMOS Inverter-based architecture has been found as an alternative method, in literature, for realizing OTAs (Figueiredo et al. 2011, Shrimali and Chatterjee 2011, Michel and Steyaert 2012, Wilson et al. 2013, Luo et al. 2013b, Harjani and Palani 2015, Lee et al. 2016, de Aguirre and Susin 2018). Such OTAs have been seen as a replacement for traditional OTA's, especially for Switched-Capacitor (SC) applications. The idea here is to use a CMOS inverter, operated at a point on the transfer characteristics where the slope is maximum. The inverter being a single ended amplifier, the differential operation, if any, has to be realized using pseudo-differential architecture and has been the case as per the literature. A CMOS inverter has a poor gain, making it unsuitable for OTA applications. The CMOS inverters are found to be used with cascode transistors and additional gain boosting stages to have dc gain sufficiently high enough to be used as OTAs (Luo et al. 2013b, Lee et al. 2016). Due to the single stage structure and simplicity, this kind of architecture is found to be a promising candidate for OTA realization, especially for SC applications.

This research is an outcome of the efforts of designing an inverter-based low power OTA to offer dc gain in excess of 80 dB and stability with a very good margin, for SC applications. The major contributions of this research work are given in the following section.

### 1.2 CONTRIBUTIONS

The research proposes an architecture for realizing inverter-based high gain OTAs intended for supply voltages more than sum of threshold voltages of NMOS and PMOS transistors i.e.  $V_{TH,n} + |V_{TH,p}|$ . A detailed analysis on the design aspects and stability has been presented. The proposed architecture has been validated by designing OTAs in 180 nm standard CMOS process for operation on 1.8V supply. Two designs have been presented. The first design with a dc gain of 109.3 dB is targeted for biomedical applications. The OTA has been designed to have a unity gain bandwidth (UGB) in excess of 3 MHz for a load capacitance ( $C_L$ ) of 2.5 pF with power consumption of  $8.62 \,\mu$ W. The second OTA has been targeted for audio applications. The OTA is intended for use in SC loop filter of discrete-time DSM (DTDSM). The OTA is designed to offer 96.8 dB dc gain with UGB of 19.4 MHz for  $C_L=5 \,\text{pF}$ . In both the cases, the OTAs are stable with phase margin in excess of 80° without any explicit compensation. Thanks to the single stage architecture.

A 1-bit third order DTDSM has been designed using the second OTA to prove that the proposed design fits well for SC applications. A feed-forward architecture has been chosen for implementing the loop filter of DTDSM. The DTDSM, for audio applications, is proved to be one of the best among the state-of-the-art designs offering a peak Signal to Noise and Distortion Ratio (SNDR) of 87.7 dB.

One of the power hungry analog systems in many of the portable electronics is the audio amplifier. The efficiency of such amplifiers is crucial from the battery life perspective. A Class-D amplifier (CDA) is best in its class with respect to efficiency. However, one of the limiting factor in achieving the efficiency is the power consumption in the control circuit. The proposed OTA, having low power, has been tested for its candidature in CDA. A CDA using DTDSM loop has been designed for  $8 \Omega$ speaker load. The CDA achieved an efficiency of 92.3% with an A-weighted peak Total Harmonic Distortion plus Noise (THD+N) of -90.3 dB, again one among the best in class.

### 1.3 PRIOR WORK

The OTA being the basic building block, various architectures have been proposed in the literature. Requirement on the OTA is different for different applications. However, in this research, the OTA design is targeted for switched capacitor applications that do not demand rail-to-rail swing. For application like DTDSM, the swing requirement on SC integrators (and hence the OTA) can be relaxed with a careful choice of filter coefficients. Further, the dc gain of an OTA determines the accuracy of charge transfer in the SC circuits (Quinn and van Roermund 2007). Therefore, it is essential for SC circuits to have an OTA that offers sufficiently high dc gain in order to ensure charge transfer with a desired accuracy. This research also targets OTA design for such applications. Some of the 2-stage OTA designs found in literature are presented here.

A two stage body-input OTA is presented in Chatterjee et al. (2005). It offers a dc gain of 62 dB and UGB of 10 MHz with a phase margin (PM) of 45° for a load capacitance  $C_L$  of 20 pF. A Figure-of-Merit (FoM), computed using (1.16), is found to be  $1333 \,\mathrm{kV}^{-1}$ .

$$FoM = \frac{UGB (MHz) \times C_L (pF)}{I_Q (mA)}$$

(1.16)

Perez et al. (2009) presents a two-stage OTA with enhanced slew rate designed in 180 nm process. It has a simple differential amplifier first stage and a common-source second stage. The OTA, operating on 1.8 V has a dc gain of 74 dB with a phase

margin (PM) of about 70°. The UGB is 160 MHz with a power of  $362 \,\mu\text{W}$  for a load capacitance  $C_L$  of 1.75 pF. FoM of this OTA is found to be  $773 \,\text{kV}^{-1}$ .

An OTA with a simple differential amplifier first stage and a common-source amplifier with cascode transistors as second stage has been presented in Kang et al. (2008) and has been used in a CDA with DSM based control loop. The OTA offered 76 dB dc gain, 78° PM and 110 MHz UGB for  $C_L$  of 1.85 pF. The OTA is operated on 3 V supply and achieves an FoM of 291 kV<sup>-1</sup>.

The differential input, single ended output OTA presented in Moallemi and Jannesari (2012), targeted for SC applications, has a telescopic cascode first stage and a simple differential second stage. Designed in 180 nm process, the OTA is capable of offering a dc gain of 77 dB with PM of only 45°. Though it is found to offer a UGB of 475 MHz, the power requirement was 5.1 mW for a  $C_L$  of 3 pF resulting in FoM of  $503 \text{ kV}^{-1}$ .

An OTA offering 114 dB dc gain has been presented in Najjarzadegan et al. (2015). The OTA designed in 180 nm has an UGB of 305 MHz consuming a power of 4.3 mW. The FoM of this OTA is found to be  $635 \text{ kV}^{-1}$ .

The OTAs presented in Farsani and Ghaderi (2016), Sarkar and Panda (2017) are designed in 180 nm process and they offer a dc gain of 90.7 dB and 87.7 dB respectively. However they have relatively poor FoM of  $71 \,\mathrm{kV^{-1}}$  and  $70 \,\mathrm{kV^{-1}}$ .

In Daoud et al. (2016), a gain-boosted telescopic OTA has been presented which has been used in DTDSM targeted for a signal bandwidth of 2 MHz and 3.84 MHz. Though the dc gain offered by the OTA is 96 dB, with a UGB of 487 MHz, the FoM was found to be only  $57 \,\mathrm{kV}^{-1}$ .

The OTA in Pourashraf et al. (2017) offers a FoM of  $1627 \,\mathrm{kV^{-1}}$ . It is a two-stage OTA and both the stages have cascode architecture. The dc gain offered is  $67 \,\mathrm{dB}$  with a UGB of  $570 \,\mathrm{kHz}$  while consuming  $14.5 \,\mu\mathrm{W}$  power from  $\pm 0.9 \,\mathrm{V}$  supply.

The OTA presented in Garradhi et al. (2018) has 77 dB dc gain with a FoM of  $358 \,\mathrm{kV^{-1}}$ . The PM is found to be only 40°. It has a two stage architecture with a differential first stage and a cascode second stage.

Lopez-Martin et al. (2017) presents an OTA offering FoM as large as 5541 kV<sup>-1</sup>. The OTA is designed to drive  $C_L$  of 70 pF with a power of 120  $\mu$ W. However, despite being a single stage amplifier, the PM achieved is 60° due to the folded cascode architecture. The dc gain of the OTA is 81.7 dB.

|                     | Kang et al. (2008) | Perez et al. (2009) | Moallemi and Jannesari (2012) | Najjarzadegan et al. (2015) | Daoud et al. (2016) | Farsani and Ghaderi (2016) | Pourashraf et al. $(2017)$ | Sarkar and Panda (2017) | Garradhi et al. (2018) |

|---------------------|--------------------|---------------------|-------------------------------|-----------------------------|---------------------|----------------------------|----------------------------|-------------------------|------------------------|

| Supply (V)          | 2                  | 1.8                 | -                             | -                           | 1.4                 | 1.8                        | $\pm 0.9$                  | $\pm 1.8$               | $\pm 0.6$              |

| DC Gain (dB)        | 76                 | 74                  | 77                            | 114                         | 96                  | 90.7                       | 67                         | 87.7                    | 54                     |

| UGB (MHz)           | 110                | 160                 | 475                           | 305                         | 487                 | 995                        | 0.57                       | 24.8                    | 4                      |

| PM (°)              | 78                 | 70                  | 45                            | 61                          | -                   | 82                         | 84                         | 65                      | 40                     |

| $C_L (\mathrm{pF})$ | 1.85               | 1.75                | 3                             | 5                           | 1                   | 0.5                        | 23                         | 1                       | 1                      |

| Power $(\mu W)$     | 2100               | 362                 | 5100                          | 4300                        | 12000               | 12600                      | 14.5                       | 318.6                   | 40                     |

| FOM $(kV^{-1})$     | 291                | 773                 | 503                           | 635                         | 57                  | 71                         | 1627                       | 70                      | 358                    |

Table 1.2: Performance summary of 2-stage OTAs found in literature

Performance summary of these OTAs are presented in Table 1.2. For a good DTDSM design, the OTA should be chosen to have dc gain in excess of 80 dB (Pavan et al. 2017). This will help in keeping all distortion terms to sufficiently low level  $\approx$  -90 dBc. In the light of this, the following conclusions can be made from the OTAs found in the literature as presented above.

- 1. The OTAs that are found to offer dc gain in excess of 80 dB suffer from poor FoM, except one. The OTA presented in Lopez-Martin et al. (2017) has a dc gain 81.7 dB and FoM 5541 kV<sup>-1</sup>. However, it is to be noted that, the OTA is designed for a large capacitive load of 70 pF. For low values of  $C_L$  the phase margin will definitely degrade below 60°.

- 2. The OTAs having FoM in excess of FoM of 500  $kV^{-1}$  are found to have either dc gain less than 80 dB or consume more power (in the order of mW).

A CMOS Inverter-based architecture has been found to replace the traditional architecture for realizing OTAs. In literature, these OTAs have been found to be used in a few applications and some of them are listed below. An inverter-based OTA has been proposed in Chae and Han (2009) for DSM application for audio band. The OTA designed in 180 nm has been operated on 0.7 V. With cascode architecture, the dc gain is found to be 60 dB. The third order DTDSM designed, using this OTA, is found to offer a peak SNDR of 81 dB for an OSR of 100.

A two-stage fully differential inverter-based OTA employing self-biasing techniques is presented in Figueiredo et al. (2011). The OTA is designed in 130 nm standard CMOS technology and operates on 1.2 V. It offers a gain of 70 dB with a UGB of 35 MHz and PM of 45° for a  $C_L$  of 5.5 pF. The OTA consumes a power of 110  $\mu$ W.

A three-stage inverter-based OTA with feed-forward compensation technique is presented in Shrimali and Chatterjee (2011). The OTA is designed in 130 nm standard CMOS technology and it is operated on 1.2 V. Despite being a three stage design, the gain offered is only 39.5 dB. However, it offers a UGB of 11 GHz with 62° PM for a  $C_L$  of 600 fF. The power consumption of the OTA is 18 mW.

A simple inverter has been used as OTA in a DTDSM in Michel and Steyaert (2012). The OTA is designed in 130 nm standard CMOS technology. The gain realized from the OTA operating on a supply voltage of 250 mV is only 30 dB with a UGB of 6.3 MHz for  $C_L$  of 3 pF. The third order DTDSM, for signal band of 10 kHz, offered a peak SNDR of 61 dB for an OSR of 70.

Wilson et al. (2013) proposed a fully differential, low-power current-starving inverterbased amplifier topology designed in 180 nm process. It achieves a dc gain of 48.3 dB with a UGB of 2.4 MHz for a  $C_L$  of 6 pF, while operating on 0.9 V. Its power consumption is  $3.74 \,\mu\text{W}$ .

The OTA presented in Luo et al. (2013b) has been used for DTDSM designed to operate on 0.8 V in 65 nm CMOS process technology. The OTA, employing cascode transistors with gain-boosting, is found to offer 83 dB dc gain and 49 MHz UGB for a 5.75 pF  $C_L$ . The DTDSM designed for audio band has a 2-1 cascaded architecture and offers a peak SNDR of 91 dB for an OSR 128. It is found that, the OTA uses body bias technique for both PMOS and NMOS transistors of the inverter, which requires a tripple-well CMOS process technology.

A 2-1 cascaded DTDSM, designed in 130 nm CMOS process, in Luo et al. (2013a) presents an inverter-based OTA. It uses cascode transistors along with gain-boosting technique to achieve a dc gain of 67 dB operating on 1.2 V supply. The UGB is

45.3 MHz for 1.5 pF  $C_L$ . As in Luo et al. (2013b), this design also requires a tripplewell process.

A PVT tolerant inverter based OTA, designed in 65 nm CMOS process technology, has been presented in Harjani and Palani (2015). It uses a three stage design. The first stage does the common-mode rejection, the second stage employs cascode architecture for achieving higher gain and the third stage is a miller compensated driver stage. All the stages are biased with the constant gm biasing technique. The proposed OTA offers around 62 dB gain and UGB of around 101 MHz with PM of 62° for a 1 pF  $C_L$ .

An adaptive-biased inverter-based OTA has been presented in Gönen et al. (2016). The inverter using cascode transistors are biased adaptively so as to keep the current to  $125 \,\mu\text{A}$  for a dc gain of 65 dB. The OTA is used in a Zoom-ADC that employs a combination of an asynchronous SAR ADC and a free-running 1b DSM. The course output from the SAR ADC is used to continuously update the references of DSM. The ADC, designed in 180 nm CMOS technology, achieved a peak SNDR of 98.3 dB for audio band with a sampling frequency of 11.29 MHz.

An improved version of the OTA proposed in Gönen et al. (2016) has been presented in Lee et al. (2016). The adaptive biasing scheme has been modified and the quiescent current has been kept to  $50 \,\mu$ A. A third order DTDSM realized using this OTA, in silicon, for audio band offered a peak SNDR of 97.7 dB with an OSR of 128.

de Aguirre and Susin (2018) presents a third order continuous-time DSM (CTDSM) based on single stage inverter-based OTA. Operating on 0.6 V, the OTA provides a dc gain of 38.4 dB with UGB of 14.4 MHz with PM of 90° for a  $C_L$  of 8 pF. Its consumes a power of  $40.1 \,\mu$ W.

Inverter-based OTAs are also used in the design of CTDSMs (Wang et al. 2013, Essawy and Ismail 2014, Irfansyah et al. 2015, Ismail and Mostafa 2016) and filter designs (BarthÚlemy et al. 2008, Braga et al. 2019).

The performance summary of some of these inverter-based OTAs is presented in Table 1.3. It is found that inverter-based OTAs have been used for designs operating on lower supply voltage and they consume power in excess of  $50 \,\mu\text{A}$  when operated at higher supply voltages (VDD > 1 V) despite the fact that these inverter-based OTAs do not provide dc gain in excess of 80 dB except Luo et al. (2013b).

SC circuit based data converters, operating on supply voltages greater than 1 V, are used in the design of several portable, battery powered electronic applications such as digital microphones (Le et al. 2010, Thomas 2013), bio-sensors (Agah et al.

|                     | Figueiredo et al. (2011) | Shrimali and Chatterjee (2011) | Michel and Steyaert (2012) | Wilson et al. (2013) | Luo et al. (2013a) | Luo et al. (2013b) | Harjani and Palani (2015) | Lee et al. (2016) | de Aguirre and Susin (2018) |

|---------------------|--------------------------|--------------------------------|----------------------------|----------------------|--------------------|--------------------|---------------------------|-------------------|-----------------------------|

| Supply (V)          | 1.2                      | 1.2                            | 0.25                       | 0.9                  | 1.2                | 0.8                | 0.9                       | 1.8               | 0.6                         |

| DC Gain (dB)        | 70                       | 39.5                           | 30                         | 48.3                 | 67                 | 83                 | 62                        | 60                | 38.4                        |

| UGB (MHz)           | 35                       | 11000                          | 6.3                        | 2.4                  | 45.3               | 49                 | 101                       | 30                | 14.4                        |

| PM (°)              | 45                       | 62                             | -                          | -                    | -                  | -                  | 62                        | -                 | 90                          |

| $C_L (\mathrm{pF})$ | 5.5                      | 0.6                            | 3                          | 6                    | 1.5                | 5.75               | 1                         | 5.2               | 8                           |

| Power $(\mu W)$     | 110                      | 18000                          | 0.62                       | 3.74                 | 57.2               | 34.5               | 6.3                       | 90                | 40.1                        |

| FOM $(kV^{-1})$     | 2100                     | 440                            | 7620                       | 3465                 | 1425               | 6533               | 14428                     | 3120              | 1723                        |

Table 1.3: Performance summary of inverter-based OTAs found in literature

2010, Hall et al. 2013, Van Helleputte et al. 2015), image sensor (Chae et al. 2011), data acquisition systems (Liu et al. 2012, Lee et al. 2015), hearing aids (Porrazzo et al. 2013, Custódio et al. 2013, Noh et al. 2013), etc. Such applications require lowpower designs, which would result in a relatively cooler devices with longer battery run time. Also, it is common to operate analog signal processing blocks on a higher supply (available for IO) to take advantage of head room available, even though the digital circuitry are operating on low supply voltages. For designs like DTDSM based CDAs, the inverter is required to offer gains in excess of 80 dB and at the same time keep the quiescent current to a sufficiently low value.

Inverter-based OTAs for SC applications, operating on higher supply voltages requires a re-look into the design. An OTA that delivers high dc gain with lower power consumption is the necessity and designing such an OTA is quite challenging. Any research contribution in this direction is considered to be worth the effort. The OTA design is targeted for two applications namely bio-medical applications and audio applications, covering both the front-end and back-end categories.

### 1.4 ORGANIZATION OF THESIS

The thesis has been organized as follows.

The chapter 2 proposes the inverter-based OTA architecture for realizing a very high gain. It also gives a detailed analysis of the achitecture, its stability and design steps.

The chapter 3 is dedicated for the design of OTA using the proposed architecture. It presents two OTAs for biomedical and audio applications along with all necessary simulation results.

The chapter 4 presents the design of the DTDSM. After a brief introduction to DTDSM, the chapter outlines the design of SC based implementation of the DTDSM. The circuit design and implementation of each and every block of DTDSM has been presented and the chapter is concluded with the simulation results.

In chapter 5, an on-chip CDA design has been presented. With a brief introduction to CDA, the chapter outlines the design of a DSM based CDA. The design of fullbridge power stage has been outlined along with the driving schemes. Simulation results are presented at the end of the chapter.

Conclusion are drawn in chapter 6, along with the scope for future research.

## Chapter 2

# INVERTER-BASED OTA AND ITS DESIGN ANALYSIS

### 2.1 CMOS INVERTER AS AN OTA

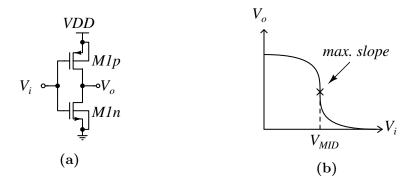

A simple CMOS inverter formed using a NMOS and a PMOS, shown in Figure 2.1a, can act as single-ended amplifier. The slope of the voltage transfer characteristics (VTC) at a given point on the VTC is gain offered by amplifier. Therefore, to obtain maximum gain for a given inverter, the operating point should be at a point on the VTC where the slope is maximum, as shown in Figure 2.1b. In this figure, it can be seen that the magnitude of the slope of VTC reaches maximum when the input  $V_i$  is set at the voltage  $V_{MID}$ . Or in other words, inverter when biased at  $V_{MID}$  offers the maximum gain.

Another point to note here is that the slope of VTC is negative at any operating point, due to which the output for an input sinusoid is 180° out of phase with respect to the input. Therefore, one can easily build a negative feedback around this amplifier by using a feedback network. If the gain offered by inverter amplifier is made sufficiently large enough, then the closed loop gain can be made to be solely decided by the feedback factor.

The small signal DC gain offered by the CMOS inverter in Figure 2.1a is given in (2.1) where  $g_{m1p}$  and  $g_{m1n}$  are the tranconductance of transistors M1p and M1n

Figure 2.1: CMOS inverter(a) Schematic circuit (b) VTC

respectively and  $g_{o1p}$  and  $g_{o1n}$  are their output conductances.

$$A_{v,simple} = \frac{g_{m1p} + g_{m1n}}{g_{o1p} + g_{o1n}}$$

(2.1)

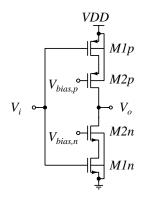

The gain  $A_{v,simple}$  is not sufficiently large enough for the inverter to be used as an OTA. For the inverter designed in 180 nm a DC gain in the range 20-35 dB can only be expected. However, with some modifications and additional circuits the gain of the inverter can be enhanced. Cascoding technique, the common approach used to improve the output impedance of a transconductor, can be readily adopted to CMOS inverter amplifier too. Figure 2.2 shows the schematic circuit of a cascoded inverter. The resulting gain of the circuit is given in (2.2). Here, the two cascode bias voltages  $V_{biasp}$  and  $V_{biasn}$  should be additionally generated.

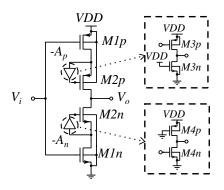

Figure 2.2: Schematic circuit of cascoded inverter (Luo et al. 2013b)

$$A_{v,cascode} = \frac{g_{m1p} + g_{m1n}}{\frac{g_{o1p}g_{o2p}}{g_{m2p}} + \frac{g_{o1n}g_{o2n}}{g_{m2n}}}$$

(2.2)

The DC gain can further be increased by employing gain-boosting technique with the help of two amplifiers of gains  $-A_p$  and  $-A_n$  realized using a common-source stage. Schematic of this modified amplifier is shown in Figure 2.3 and the overall gain is given in (2.3)

$$A_{v,gain\,boost} = \frac{g_{m1p} + g_{m1n}}{\frac{g_{o1p}g_{o2p}}{g_{m2p}A_p} + \frac{g_{o1n}g_{o2n}}{g_{m2n}A_n}}$$

(2.3)

Figure 2.3: Schematic of an inverter with gain-boosting (Luo et al. 2013b)

The gate-source voltage of transistors M1p and M1n, when the input is set at  $V_{MID}$  is,

$$V_{SG,1p} = V_{DD} - V_{MID} \tag{2.4}$$

$$V_{GS,1n} = V_{MID} \tag{2.5}$$

$V_{MID}$  and  $V_{DD}$  are the voltages that sets the bias for M1p and M1n which in turn sets the quiescent current in the inverter. For low power applications, the quiescent current should be kept at low values. Often, low quiescent current is set by maintaining the transistors in the weak inversion region. Operating the transistors in weak inversion has another advantage, which is, for a given drain current, the transconductance offered by the transistor is higher than that of the transistor operated in strong inversion. This is explained as follows.

Consider an NMOS transistor operated in strong inversion region  $(V_{GS} > V_{TH})$ and biased in saturation  $(V_{DS} \ge V_{GS} - V_{TH})$ . Where  $V_{GS}$  is the gate-source bias voltage,  $V_{DS}$  is the drain-source voltage and  $V_{TH}$  is the threshold voltage of the transistor. The transconductance of the transistor, for a given aspect ratio, is given by (2.6)

$$g_{m,SI} = \frac{2I_D}{(V_{GS} - V_{TH})}$$

(2.6)

Where  $I_D$  is the drain current.

For a transistor operated in weak inversion, the transcondutance offered by the transistor is approximated as in (2.7)

$$g_{m,WI} = \frac{I_D}{\eta V_T} \tag{2.7}$$

Where,  $V_T$  is the volt-equivalent of temperature (or thermal voltage) having a value  $\approx 26 \text{ mV}$  at room temperature.  $\eta = \frac{C_{ox} + C_{dep}}{C_{ox}}$  and it is a process dependent parameter ( $\approx 2/3$  in weak inversion).

Assuming that the gate overdrive  $V_{GS} - V_{TH}$  is maintained at atleast 100 mV, from (2.6) and (2.7), it can be clearly inferred that  $g_{m,WI}$  can easily be more than three times of  $g_{m,SI}$ . Therefore, operating transistor in weak inversion has a clear advantage of power and gain. However, this comes at the expense of signal swing.

For maintaining the transistors in weak inversion it is required that  $|V_{GS}| \leq |V_{TH}|$ . This requirement poses serious limitation on the maximum  $V_{DD}$  that can be used i.e.,  $V_{DD} < V_{TH,n} + |V_{TH,p}|$ . At higher supply voltages,  $|V_{GS}| \geq |V_{TH}|$  and the transistors cannot be operated in weak inversion. The quiescent current through M1p and M1ntransistors can be significantly high since their gate overdrive voltage can be quite high or in other words, to achieve a given transconductance  $(g_m)$ , these inverters have to burn more power than in the case when they are operated in weak inversion. Therefore, these inverters are not power efficient at higher supply voltages and hence not suitable for low power applications.

This research proposes an architecture for inverter-based OTA to realize high DC gain while keeping the quiescent current to a low value.

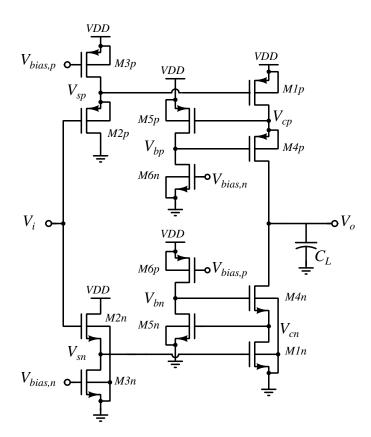

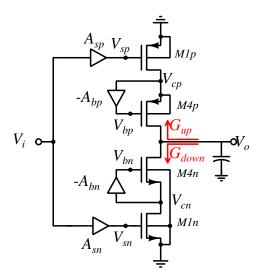

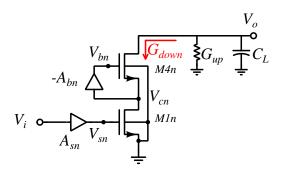

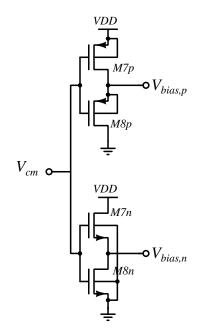

### 2.2 PROPOSED OTA

In order to retain the advantages of operating the inverter in weak inversion even when operated at higher supply voltage, two source follower circuits with active load have been added to the signal path. The complete schematic of the proposed inverter-based gain-boosted OTA (IGB-OTA) is shown in Figure 2.4. Cascoding and gain-boosting techniques are used to achieve a higher DC gain. The PMOS and NMOS transistors, M1p and M1n respectively, form the inverter. The inverter transistors are cascoded with M4p and M4n to increase the effective output impedance of the inverter and thereby achieves a higher small signal voltage gain. The gain is further improved using gain-boosting technique (Bult and Geelen 1990). Common-source amplifiers formed by transistors M5p, M6n and M6p, M5n offer gain-boosting.