# A DIGITAL HEARING AID ASIC WITH EFFICIENT 18-BAND ANSI S1.11 FILTER BANK AND DYNAMIC RANGE COMPRESSION ALGORITHMS

Thesis

# Submitted in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

by DEEPU S. P.

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING, NATIONAL INSTITUTE OF TECHNOLOGY KARNATAKA, SURATHKAL, MANGALORE -575025

DECEMBER 2020

# DECLARATION

I hereby *declare* that the research thesis entitled A Digital Hearing Aid ASIC with Efficient 18-Band ANSI S1.11 Filter Bank and Dynamic Range Compression Algorithms which is being submitted to the *National Institute of Technology Karnataka, Surathkal* in partial fulfillment of the requirement for the award of the degree of *Doctor of Philosophy* in Department of Electronics and Communication Engineering is a *bona fide report of the research work carried out by me*. The material contained in this research thesis has not been submitted to any University or Institution for the award of any degree.

> Deepu S. P., Register No.: 148050EC14FV10 Department of Electronics and Communication Engg.

Place: NITK Surathkal. Date: 31-12-2020

# CERTIFICATE

This is to certify that the research thesis entitled **A Digital Hearing Aid ASIC with Effi**cient 18-Band ANSI S1.11 Filter Bank and Dynamic Range Compression Algorithms, submitted by Deepu S. P. (Register Number: 148050EC14FV10) as the record of the research work carried out by him, is accepted as the *research thesis submission* in partial fulfillment of the requirements for the award of degree of Doctor of Philosophy.

> Dr. Sumam David S. Research Guide Professor Department of Electronics and Communication Engg. NITK Surathkal - 575025

> Dr. Ramesh Kini M. Research Guide Associate Professor Department of Electronics and Communication Engg. NITK Surathkal - 575025

> > **Chairman - DRPC** (Signature with Date and Seal)

### Acknowledgements

I feel immense pleasure in expressing my profound sense of gratitude to my thesis supervisors Prof. Sumam David S. and Dr. Ramesh Kini M. for providing me the opportunity to work with them over the past few years. I consider myself very blessed to have them as my mentors. Both of them always made sure that I have access to the best facilities available at NITK for carrying out my research. They always encouraged me to explore more on newer topics and provided ample opportunities to attend many workshops and trainings to learn advanced tools and hardware kits. They have never stopped me from trying out my own ideas and given immense freedom to do research the way I want. Both my supervisors allowed me to take enough time to carry out my work which really helped to overcome the difficult times when things don't work out the expected way. They have always considered my view and suggestions with its due merit on a few technical matters, and such gestures were big confidence booster for me as a student. I would like to take this opportunity to express my heartfelt thanks to both of them for taking care of me throughout my stay at NITK.

I extend my gratitude towards my research progress assessment committee members Dr. A.V. Narasimhadhan and Dr. Gangadharan K.V. Their suggestions and inputs were valuable to improve various aspects of this research work. I would like to thank our head of department Prof. T. Laxminidhi and former department heads Prof. M. S. Bhat and Prof. U. Sripathi for their support and help in my research work. I would also like to thank faculty members at NITK with whom I have had the opportunity to take courses. There is massive support from many people at NITK to carry out my research. I would like to take this opportunity to thank each one of them.

I would like to express my deep gratitude towards Mrs. N. S. Prabha, the lab assistant in the DSP lab for her support throughout my journey at NITK. Prabha ma'am has a deep impact on my life at NITK, who was always there for me with any kind of assistance needed related to lab resources and tool setups. More than technical, emotional support I got from her can't be expressed in words. Another person I should mention here is my fellow researcher Dr. Anu Shaju Areeckal. The care she provided as my senior was invaluable and always stood by me as a helping hand. She was my go-to person if I face any kind of

problem. She kept me motivated towards my work whenever I felt down with the research outcome. I would like to take this opportunity to thank her also from the bottom of my heart for all the good words and the genuine support provided as my lab companion.

The support provided by all those undergraduate students of the ECE department from year to year throughout my days at NITK cannot be expressed in words. I learned many things from them regarding how to approach problems and come up with solutions. I had the opportunity to be the mentor for many of their group projects, which forced me to think on multiple problem statements at the same time and those long discussions and friendly arguments that happened with them on many topics improved my critical thinking. I am not able to name a few because the list is so long. I would like to thank each one of them also for making me a better person. I would also like to thank my colleagues Dr. Ashish Patil, Mr. Bhat Raghavendra, Mr. Prasad Naik and other research scholars for their support and help during my Ph.D. work. I especially thank my roommate Ashish for those long discussions regarding different areas along with research, from the beginning of my Ph.D.

I thank Ministry of Electronics and Information Technology (MeitY), Government of India, for providing full time research grant under the Visvesvaraya Ph.D. scheme. I also thank Special Manpower Development Program for Chips to System Design (SMDP-C2SD) under MeitY for providing support in terms of EDA tools and training through various workshops. I was lucky to meet many experts especially from the domain of VLSI during such workshops. I would like to thank all those people also who have conducted those workshops and helped me personally to clear many problems related to EDA tool usage. I thank Technical Education Quality Improvement Programme(TEQIP) at NITK for providing funding for my visit to Beijing to present my paper in the DSP-2016 conference. I also thank the School of Allied Health Sciences(SOAHS), Manipal University for demonstrating the hearing aid fitting procedure, IEEE Special Interest Group in Humanitarian Technology (SIGHT) and Centre for System Design (CSD), NITK. I thank all those people who have directly or indirectly helped me during my Ph.D. tenure.

And finally, I would like to thank all my teachers and The God Almighty for making me learn whatever little I can in this small life.

### Abstract

According to World Health Organization, 466 million people (more than 5 percent of the world population) have disabling hearing loss. A Digital hearing aid consists of analog front end and digital signal processing blocks along with transducers. The incoming sound signal captured by the microphone is given to an analog to digital converter (ADC). The digital output from the ADC is processed by the digital signal processor (DSP) and the processed signal is converted back to analog using a digital to analog converter (DAC) before sending it to the receiver. In this work, the design of a signal processing ASIC, which can perform the task of auditory compensation and the signal compression in a digital hearing aid is presented.

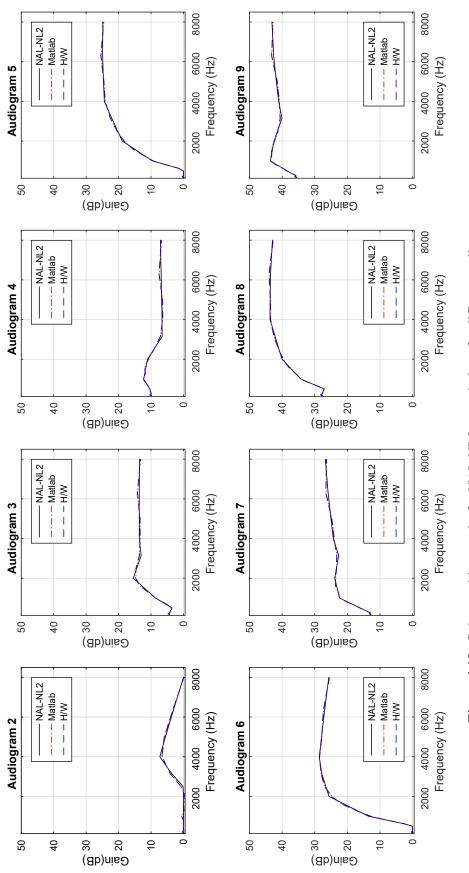

Studies on the features of current state of the art techniques suggest a requirement for further optimisation in the area of filter bank and dynamic range compression algorithms. In this work, a new filter bank architecture and new expressions addressing the effects of gain compression stage on the attack and release time decay coefficients of dynamic range compression algorithm are proposed. In dynamic range compression, by using the proposed equations for estimating the decay coefficients at the algorithm level, the errors that occur at the output with conventional method are totally removed to meet the ANSI S3.22 specifications for hearing aids. At architectural level, eight different architectures for the DRC algorithm were compared and conclusions are drawn on the selection of the features of DRC based on the hearing aid requirement. Based on the results, we propose to use an absolute level detector based DRC without smoothing stage for a low power hearing aid application. Interpolated Finite Impulse Response (IFIR) technique was used to develop the proposed 18-band ANSI S1.11 filter bank architecture. Since IFIR technique was used, the hardware implementation of the entire structure became less complex compared to other architectures. The proposed algorithm requires 50% lesser number of filter coefficients compared to other ANSI S1.11 architectures. The proposed algorithm was implemented using standard cell based design flow and the design was tested with NAL-NL2 gain prescription formula for 8 different audiograms corresponding to different hearing losses. The test results show that the maximum matching error is less than 1 dB. The major contribution of this thesis is the complete hardware implementation of 18-band ANSI S1.11

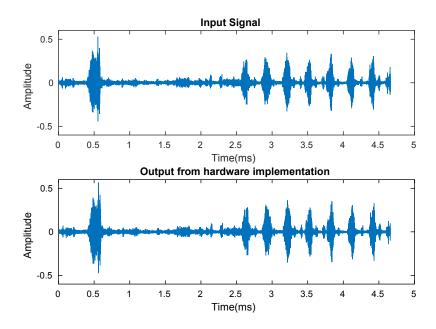

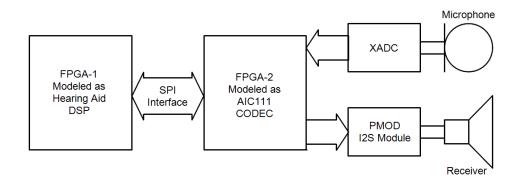

filter bank, as it is not reported in literature to best of our knowledge. The proposed filter bank combined with DRC consumes a total power of 0.39 mW for 65 nm technology. The design was verified in real-time using two FPGAs, one of them modeled as the proposed hearing aid DSP and the other as an external audio CODEC. The hearing aid chip was provided with an SPI protocol for interfacing with the external audio CODEC. The design was also ported to SCL 180 nm technology to fabricate a prototype ASIC.

# Contents

|   | Ack   | nowledgements                                            | i   |

|---|-------|----------------------------------------------------------|-----|

|   | Abst  | tract                                                    | iii |

|   | List  | of Figures                                               | vii |

|   | List  | of Tables                                                | x   |

|   | Abb   | reviations                                               | xi  |

| 1 | Intro | oduction                                                 | 1   |

|   | 1.1   | Digital Hearing Aid Block Diagram                        | 2   |

|   | 1.2   | Motivation and Research Objectives                       | 5   |

|   | 1.3   | Design Approach                                          | 7   |

|   | 1.4   | Contribution of the Thesis                               | 9   |

|   | 1.5   | Organisation of the Thesis                               | 10  |

| 2 | Revi  | iew of Digital Hearing Aids                              | 13  |

|   | 2.1   | Types of Hearing Loss                                    | 13  |

|   | 2.2   | Types of Hearing Aids                                    | 15  |

|   | 2.3   | Hearing Aid Fitting Procedure                            | 17  |

|   | 2.4   | Hearing Aid Characteristics and Definitions              | 19  |

|   | 2.5   | User Satisfaction and Problems with Current Hearing Aids | 20  |

|   | 2.6   | Hearing Aid Chip (HAC) Implementations                   | 22  |

|   | 2.7   | Filter Bank Algorithm                                    | 27  |

|   | 2.8   | Dynamic Range Compression (DRC)                          | 31  |

|   | 2.9   | Summary                                                  | 35  |

| 3 | Dyn   | amic Range Compression Algorithm                         | 37  |

|   | 3.1   | Background                                               | 38  |

|   | 3.2   | Basics of DRC Algorithm                                  | 39  |

|   |       |                                                          |     |

|    | 3.3                                | Propose   | ed Methodology for the Estimation of Decay Coefficients                      | 41   |

|----|------------------------------------|-----------|------------------------------------------------------------------------------|------|

|    |                                    | 3.3.1     | Level Detection                                                              | 41   |

|    |                                    | 3.3.2     | Gain Calculation                                                             | 42   |

|    |                                    | 3.3.3     | Effect of Compression Factor on Decay Coefficients, $\alpha$ and $\beta$ and |      |

|    |                                    |           | Proposed Modifications to Compensate the Effect                              | 43   |

|    |                                    | 3.3.4     | Smoothing                                                                    | 44   |

|    | 3.4                                | Hardwa    | re Implementation                                                            | 47   |

|    | 3.5                                | Results   | and Discussion                                                               | 51   |

|    |                                    | 3.5.1     | Hardware Implementation Results                                              | 52   |

|    |                                    | 3.5.2     | Error Analysis                                                               | 54   |

|    | 3.6                                | Summa     | ry                                                                           | 54   |

| 4  | Prop                               | oosed Fil | ter Bank Algorithm and Hardware Implementation                               | 57   |

|    | 4.1                                | Hearing   | g Aid Fitting and Sample Audiograms                                          | 57   |

|    | 4.2                                | Backgro   | ound                                                                         | 60   |

|    | 4.3                                | Propose   | ed Methodology                                                               | 62   |

|    |                                    | 4.3.1     | Gain Optimisation                                                            | 66   |

|    | 4.4                                | Hardwa    | re Implementation                                                            | 68   |

|    | 4.5                                | Simulat   | tion Results and Discussion                                                  | . 74 |

|    |                                    | 4.5.1     | Comparison with other Architectures                                          | . 74 |

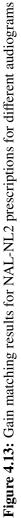

|    |                                    | 4.5.2     | Hardware Results                                                             | 76   |

|    | 4.6                                | Summa     | ry                                                                           | 79   |

| 5  | Real                               | l-time Te | esting using FPGAs and ASIC Implementation                                   | 81   |

|    | 5.1                                | Real-tir  | ne Testing using FPGAs                                                       | 81   |

|    | 5.2                                | ASIC In   | mplementation of the Proposed Hearing Aid Architecture using SCL-            |      |

|    |                                    | 180 nm    | Technology                                                                   | 87   |

|    | 5.3                                | Summa     | ry                                                                           | 90   |

| 6  | Con                                | clusions  | and Future Scope                                                             | 91   |

| RI | EFER                               | ENCES     |                                                                              | 95   |

| Pı | hlica                              | tions has | sed on the thesis                                                            | 107  |

|    | Iblications based on the thesis107 |           |                                                                              |      |

# **List of Figures**

| 1.1  | Speech banana diagram                                                                                                                                                                                                                               | 2  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1.2  | DHA block diagram                                                                                                                                                                                                                                   | 2  |  |

| 1.3  | DSP block diagram                                                                                                                                                                                                                                   | 4  |  |

| 1.4  | Frequency distribution inside cochlea                                                                                                                                                                                                               | 4  |  |

| 2.1  | Cross-section of human ear                                                                                                                                                                                                                          | 14 |  |

| 2.2  | Types of hearing aids                                                                                                                                                                                                                               | 16 |  |

| 2.3  | Hearing aid fitting procedure                                                                                                                                                                                                                       | 19 |  |

| 2.4  | Gain compression curve (Abel and Berners (2003))                                                                                                                                                                                                    | 34 |  |

| 3.1  | Dynamic range compression (DRC) pictorial representation (Banerjee (2011))                                                                                                                                                                          | 37 |  |

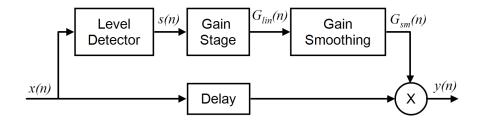

| 3.2  | Basic block diagram of a feed-forward DRC                                                                                                                                                                                                           | 40 |  |

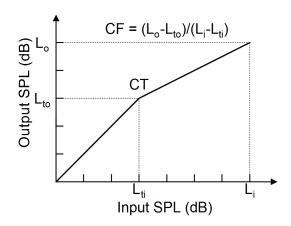

| 3.3  | Static compression curve in the log domain                                                                                                                                                                                                          | 40 |  |

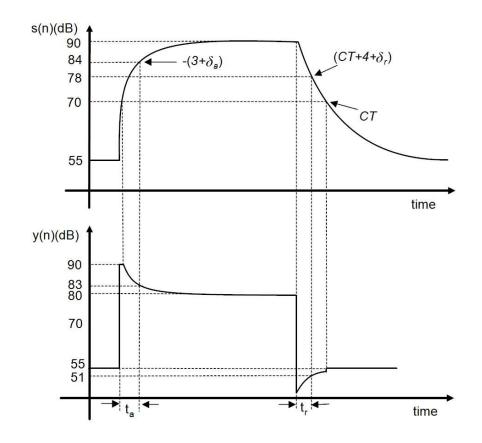

| 3.4  | Attack and release time plot corresponding to a sample estimated input                                                                                                                                                                              |    |  |

|      | curve $s(n)$                                                                                                                                                                                                                                        | 44 |  |

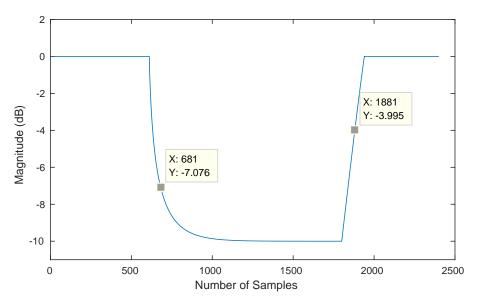

| 3.5  | Plot of the gain curve for the test signal                                                                                                                                                                                                          | 46 |  |

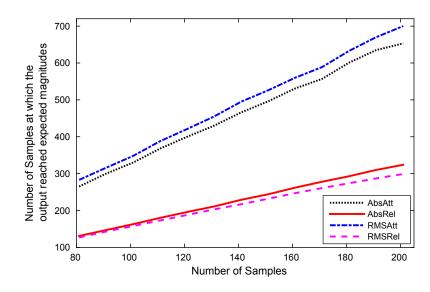

| 3.6  | Number of samples plot for attack and release phases for finding the de-<br>cay coefficients for smoothing stage. The legends can be interpreted as:<br><i>Abs</i> - Absolute detector based DRC; <i>RMS</i> - RMS detector based DRC; <i>Att</i> - |    |  |

|      | Attack phase; <i>Rel</i> -Release phase                                                                                                                                                                                                             | 47 |  |

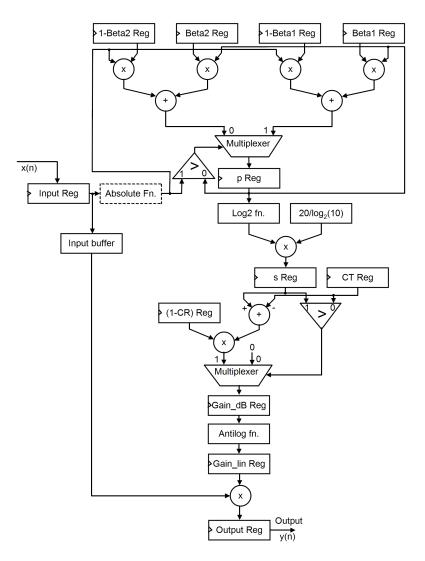

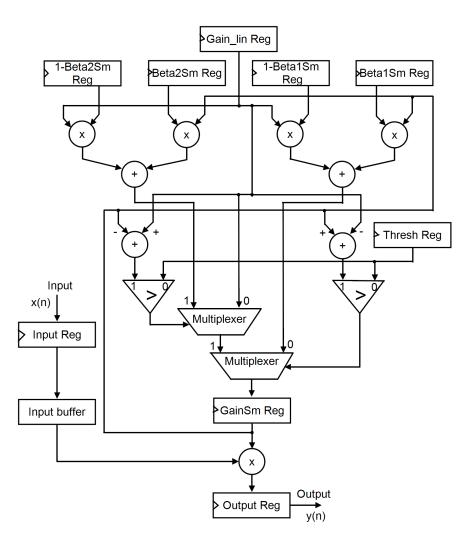

| 3.7  | Hardware architecture of the absolute detector based DRC algorithm                                                                                                                                                                                  | 48 |  |

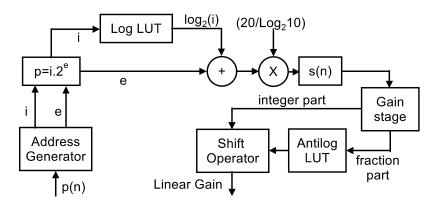

| 3.8  | LUT based logarithm implementation                                                                                                                                                                                                                  | 49 |  |

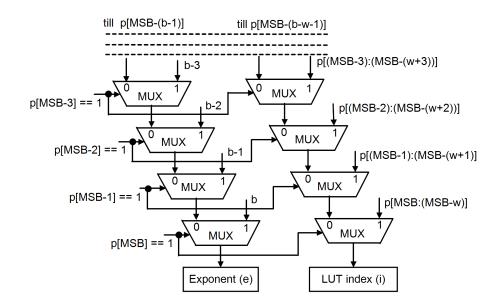

| 3.9  | Priority encoder based address generator used for logarithm table                                                                                                                                                                                   | 49 |  |

| 3.10 | Hardware architecture of the smoothing stage                                                                                                                                                                                                        | 50 |  |

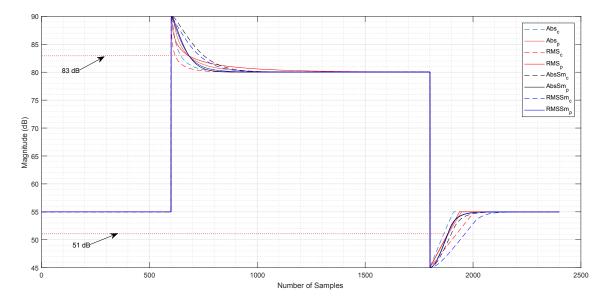

| 3.11 | Output waveforms for proposed (solid lines) and conventional (dashed lines)         |    |  |

|------|-------------------------------------------------------------------------------------|----|--|

|      | methods of decay coefficients estimation. (Figure legends can be interpreted        |    |  |

|      | as follows: Abs - Absolute detector based DRC; RMS - RMS detector based             |    |  |

|      | DRC; <i>Sm</i> - DRC with smoothing stage included; <i>c</i> - conventional method; |    |  |

|      | $_p$ - proposed method)                                                             | 52 |  |

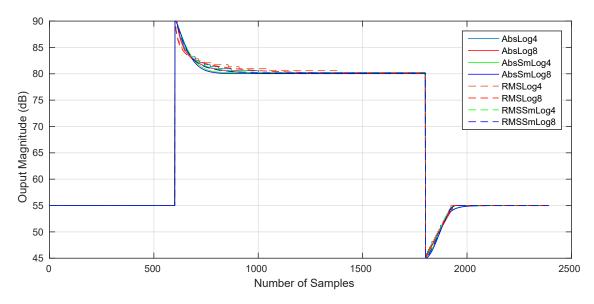

| 3.12 | Output waveforms after post-layout simulation for different architectures           | 52 |  |

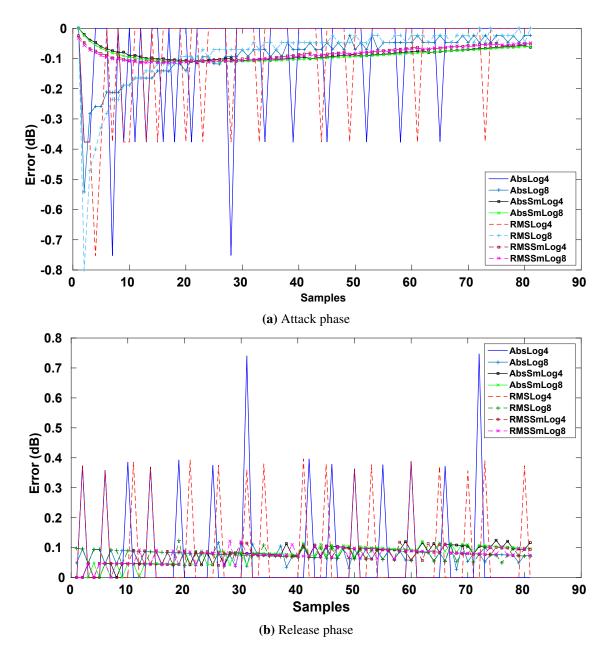

| 3.13 | Error plots during transient period for attack and release phases. (Legends         |    |  |

|      | for figures 11 and 12 can be interpreted as follows: Abs - Absolute detector        |    |  |

|      | based DRC; RMS - RMS detector based DRC; Sm - DRC with smoothing                    |    |  |

|      | stage included; Log4 - DRC implemented with 4-bit resolution logarithm              |    |  |

|      | table; <i>Log</i> 8 - DRC implemented with 8-bit resolution logarithm table.)       | 55 |  |

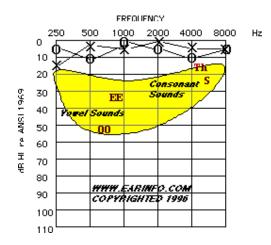

| 4.1  | Audiogram 1 - Audiogram of normal hearing (Earinfo (2014))                   |    |  |

|------|------------------------------------------------------------------------------|----|--|

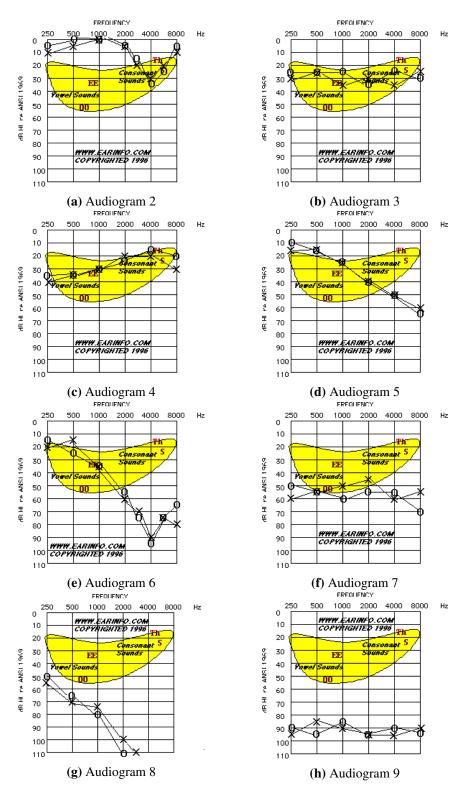

| 4.2  | Sample audiograms showing different types of hearing losses (Earinfo (2014)) |    |  |

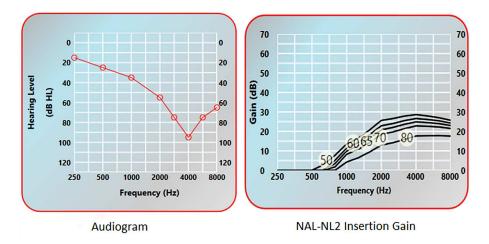

| 4.3  | A sample audiogram and its corresponding NAL-NL2 prescription gains 6        |    |  |

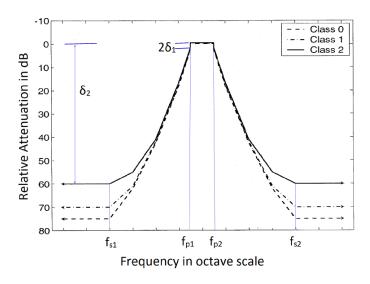

| 4.4  | ANSI S1.11 octave band specifications (ANSI (2004))                          | 61 |  |

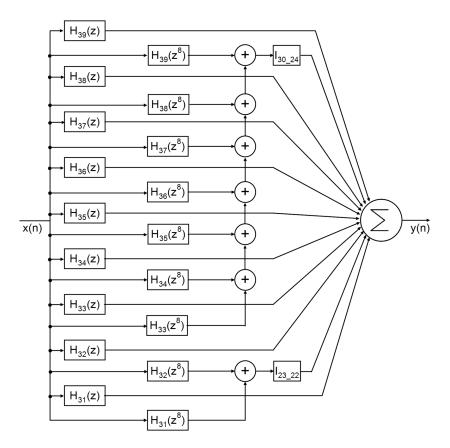

| 4.5  | Proposed filter bank architecture                                            | 63 |  |

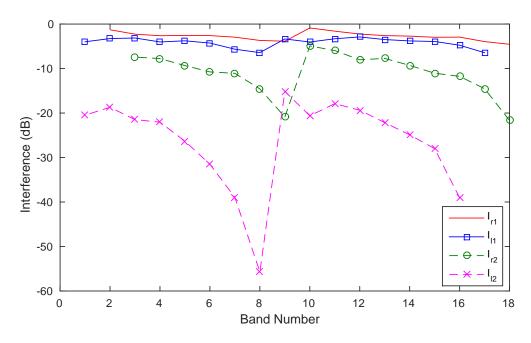

| 4.6  | Interband interference plot from neighboring bands                           | 67 |  |

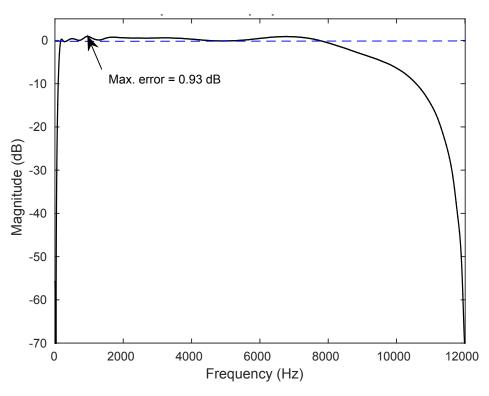

| 4.7  | Flat band response of the filter bank                                        | 68 |  |

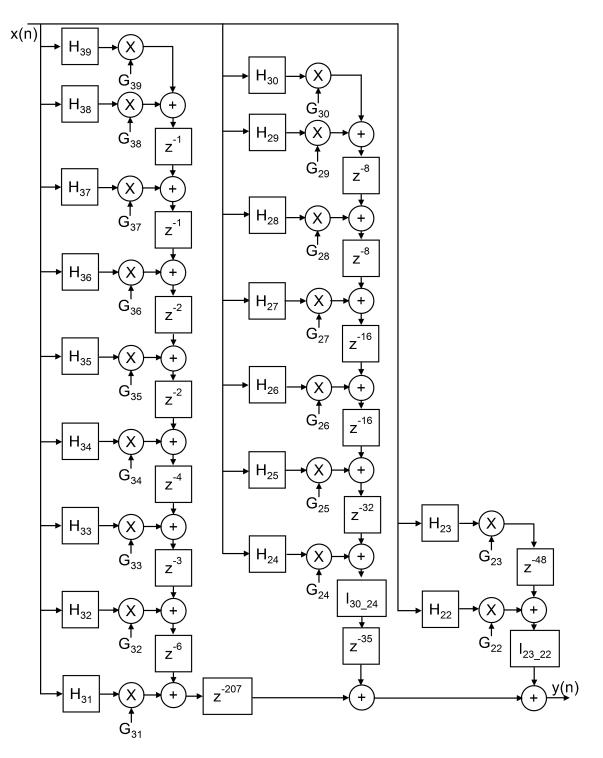

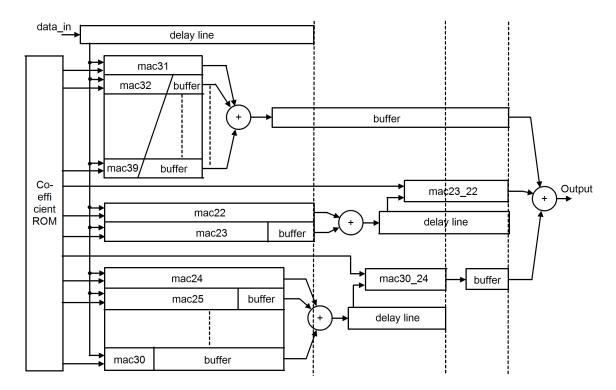

| 4.8  | Hardware realisation structure of the proposed filter bank algorithm         | 69 |  |

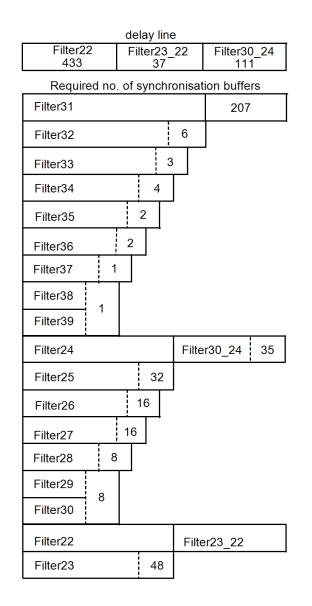

| 4.9  | Total number of synchronisation buffer and the delay line registers required |    |  |

|      | for the proposed filter bank                                                 | 71 |  |

| 4.10 | Synchronisation buffer structure of the proposed architecture                | 72 |  |

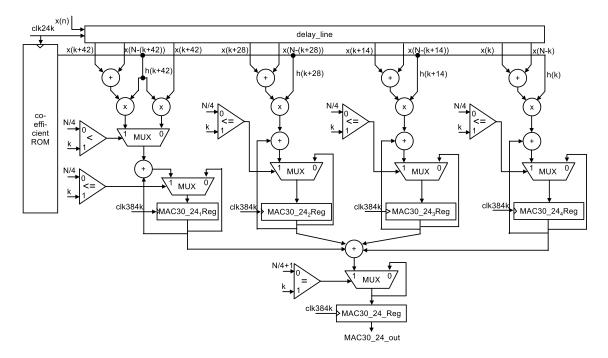

| 4.11 | Hardware architecture of the multi MAC unit of filter $I_{30.24}$            |    |  |

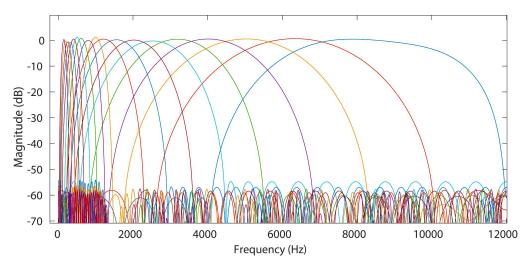

| 4.12 | Frequency response of the filter bank                                        | 74 |  |

| 4.13 | Gain matching results for NAL-NL2 prescriptions for different audiograms     |    |  |

| 4.14 | A sample audio output waveform from post layout hardware simulation          | 79 |  |

| 5.1  | Real-time testing setup of the hearing aid system using two FPGA develop-    |    |  |

|      | ment boards                                                                  | 82 |  |

| 5.2  | Top level block diagram of the experimental setup                            |    |  |

| 5.3  | Agile Mixed Signaling (AMS) connector pinout diagram of the ZedBoard (Zed-   |    |  |

|      | Board (2014))                                                                | 83 |  |

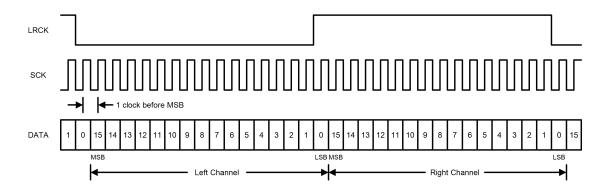

| 5.4  | Timing diagram of $I^2S$ interface $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 84 |

|------|------------------------------------------------------------------------------------------------------------|----|

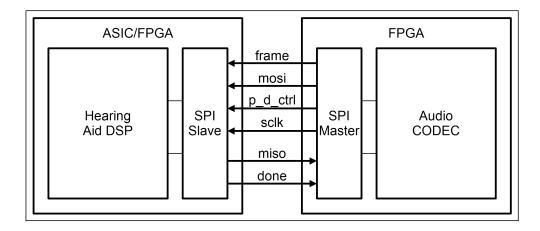

| 5.5  | SPI interface between two FPGAs                                                                            | 85 |

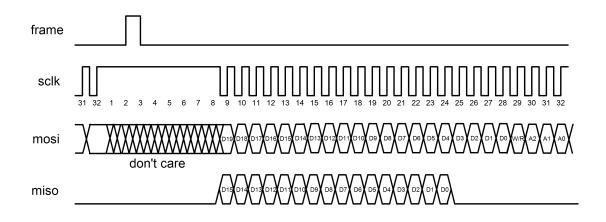

| 5.6  | Timing diagram of AIC111 SPI protocol (TI (2005))                                                          | 85 |

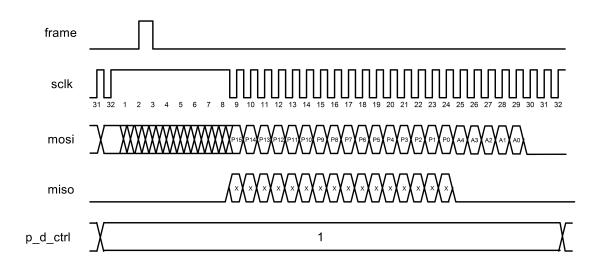

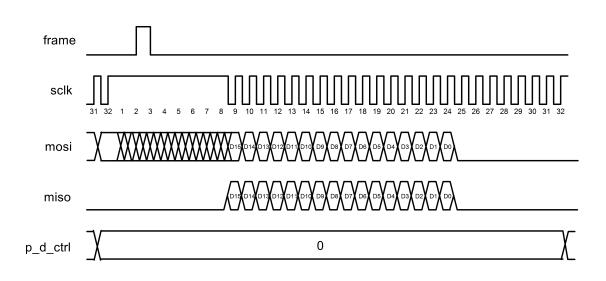

| 5.7  | SPI protocol with $p\_d\_ctrl = 1$                                                                         | 86 |

| 5.8  | SPI protocol with $p\_d\_ctrl = 0$                                                                         | 86 |

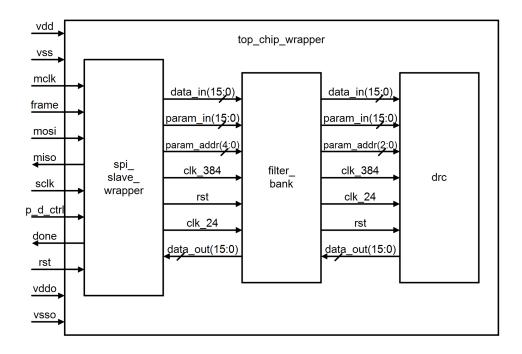

| 5.9  | Hearing aid module hierarchy                                                                               | 87 |

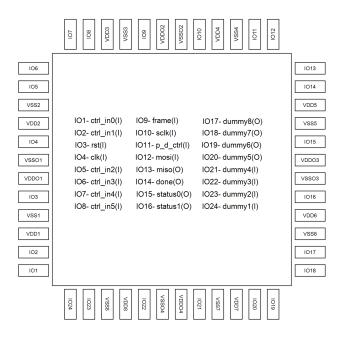

| 5.10 | Pinout diagram of the proposed hearing aid ASIC                                                            | 88 |

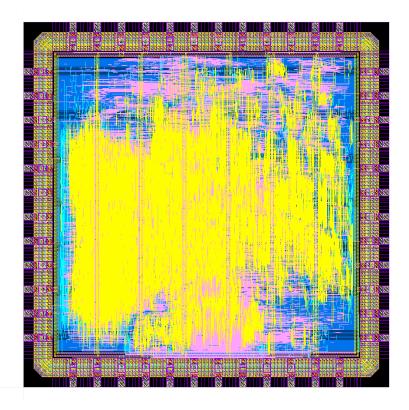

| 5.11 | Complete hearing aid ASIC layout using SCL 180 nm                                                          | 89 |

# **List of Tables**

| 2.1  | Minimum performance requirements of a hearing aid (WHO (2004))                             | 18 |

|------|--------------------------------------------------------------------------------------------|----|

| 2.2  | Various hearing aid chip implementations and their features                                | 25 |

| 3.1  | Attack and release phase decay coefficients estimated using the modified                   |    |

| 5.1  |                                                                                            | 51 |

| 2.2  | algorithm for 4 ms transient period with a 20 kHz sampling frequency                       | 51 |

| 3.2  | Output errors using conventional and proposed methods for decay coeffi-                    |    |

|      | cients estimated from output signal for the transient period of 81 samples                 |    |

|      | for attack and release phases                                                              | 51 |

| 3.3  | Power consumption for different architectures                                              | 53 |

| 3.4  | Synthesised gate count and area report                                                     | 53 |

| 3.5  | Final approximation errors estimated from the output signal for the transient              |    |

|      | period of 81 samples for attack and release phases                                         | 54 |

| 4.1  | ANSI S1.11 band edge frequencies for the filters $H_{39}$ to $H_{22}$                      | 62 |

| 4.2  | Band edge specifications for filters $H_{39}$ , $H_{31}$ and $H_{22}$ to meet the required |    |

|      | design criteria for the 18-band structure                                                  | 64 |

| 4.3  | Prototype filter specifications                                                            | 65 |

| 4.4  | Interpolation filter order exploration                                                     | 66 |

| 4.5  | Filter tap lengths and number of multiplications required for each filter                  | 70 |

| 4.6  | Operations per MAC and the required clock frequencies                                      | 73 |

| 4.7  | Comparison table                                                                           | 75 |

| 4.8  | Quantisation error (dB) due to fixed point hardware implementation com-                    |    |

|      | pared to floating point MATLAB implementation                                              | 78 |

| 4.9  | Audiogram matching error                                                                   | 78 |

| 4.10 | Operations per MAC and the required clock frequencies                                      | 78 |

|      |                                                                                            |    |

# Abbreviations

| Abbreviation | Expansion                                    |

|--------------|----------------------------------------------|

| ADC          | Analog to Digital Converter                  |

| AFE          | Analog Front End                             |

| AGC          | Automatic Gain Control                       |

| AM           | Amplitude Modulation                         |

| AMS          | Agile Mixed Signaling                        |

| ANSI         | Ameraican National Standards Institute       |

| ASIC         | Application Specific Integrated Circuit      |

| AT           | Attack Time                                  |

| BTE          | Behind The Ear                               |

| CDAC         | Centre for Development of Advanced Computing |

| CF           | Compression Factor                           |

| CIC          | Completely In Canal                          |

| CODEC        | COder DECoder                                |

| CR           | Compression Ratio                            |

| CT           | Compression Threshold                        |

| DAC          | Digital to Analog Converter                  |

| DCT          | Discrete Cosine Transform                    |

| DFT          | Discrete Fourier Transform                   |

| DHA          | Digital Hearing Aid                          |

| DRC          | Dynamic Range Compression                    |

| DSL-I/O      | Desired Sensation Level-Input/Output         |

| ECM          | Electret Condenser Microphone                |

| EDA          | Electronic Design Automation                 |

| EIN          | Effective Input Noise                        |

| ENT          | Ear Nose Throat                              |

| FB           | Filter Bank                                  |

| FBC          | Feed-Back Cancellation                       |

| FFT          | Fast Fourier Transform                       |

| FIR          | Finite Impulse Response                      |

| FM           | Frequency Modulation                         |

| FPGA         | Field Programmable Gate Array                |

| FRM          | Frequency Response Masking                   |

| GPIO         | General Purpose Input/Output                 |

| HAC          | Hearing Aid Chip                             |

| HDL          | Hardware Description Language                |

| HI           | Hearing Impaired                             |

# Abbreviations

| Abbreviation     | Expansion                                          |

|------------------|----------------------------------------------------|

| I <sup>2</sup> S | Integrated Interchip Sound                         |

| IC               | Integrated Circuit                                 |

| IFIR             | Interpolated Finite Impulse Response               |

| IHAFF            | Independent Hearing Aid Fitting Forum              |

| IIC              | Invisible In Canal                                 |

| IIR              | Infinite Impulse Response                          |

| ITE              | In The Ear                                         |

| LUT              | Look Up Table                                      |

| LSB              | Least Significant Bit                              |

| MAC              | Multiply and Accumulate                            |

| MBNR             | Modulation Based Noise Reduction                   |

| MeitY            | Ministry of Electronics and Information Technology |

| MEMS             | Micro Electro Mechanical System                    |

| MPY              | Multiplications per sample                         |

| NAL-RP           | National Acoustic Laboratory - R Profound          |

| NAL-NL           | National Acoustic Laboratory - Non Linear          |

| NR               | Noise Reduction                                    |

| OSPL90           | Output Sound Pressure Level 90                     |

| PDK              | Process Design Kit                                 |

| POGO             | Prescription of Gain/Output                        |

| QMF              | Quadrature Mirror Filter                           |

| RIC              | Receiver In Canal                                  |

| RMS              | Root Mean Square                                   |

| RT               | Release Time                                       |

| RTL              | Register Transfer Level                            |

| SCL              | Semi-Conductor Laboratory                          |

| SNHL             | Sensory Neural Hearing Loss                        |

| SNR              | Signal to Noise Ratio                              |

| SPEF             | Standard Parasitic Extraction File                 |

| SPI              | Serial Peripheral Interface                        |

| SPL              | Sound Pressure Level                               |

| TEQIP            | Technical Education Quality Improvement Programme  |

| THD              | Total Harmonic Distortion                          |

| TI               | Texas Instruments                                  |

| UMC              | United Microelectronics Corporation                |

| VLSI             | Very Large Scale Integration                       |

| WHO              | World Health Organisation                          |

| WOLA             | Weighted OverLap and Add                           |

# Chapter 1

# Introduction

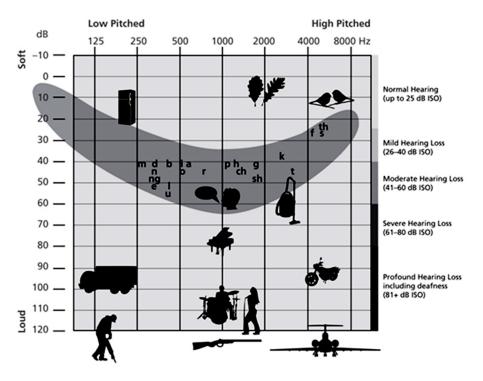

Hearing aid is a real-time system that helps people who are suffering from hearing loss. Hearing loss can be defined as partial or total inability to hear. A person having a threshold of hearing of 25 dB or more is said to have hearing loss. Based on severity level, hearing loss can be classified into mild, moderate, severe and profound. A speech banana diagram which represents the intensity and frequency of various sounds and severity of the hearing loss is shown in Figure 1.1. Different phonemes in speech, when placed in an audiogram, forms a banana-like structure. A hearing loss within speech banana can seriously affect a person's ability to perceive speech. Hearing loss can happen due to congenital and acquired reasons. Along with communication problems, the normal life of a person with hearing loss can get affected in various ways such as social, functional, emotional and economic.

According to World Health Organization (WHO), 466 million people (more than 5% of the world's population; 432 million adults and 34 million children) are suffering from disabling hearing loss (WHO (2019)). Hearing loss greater than 40 dB in the case of adults and 30 dB for children in the better hearing ear is considered as disabling hearing loss. The majority of hearing impaired (HI) live in low and middle-income countries. WHO reports also project that 900 billion teenagers and young people are at risk of hearing loss due to the unsafe use of personal audio devices including smartphones and exposure to damaging levels of sound at noisy entertainment venues. Exposure to sounds in excess of 85 dB for 8 hours and 100 dB for 15 minutes may lead to hearing impairment.

Figure 1.1: Speech banana diagram<sup>1</sup>

# 1.1 Digital Hearing Aid Block Diagram

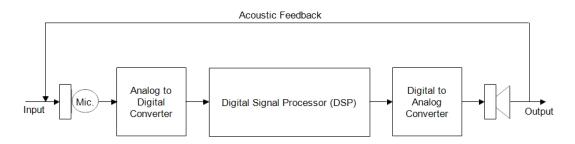

A digital hearing aid (DHA) consists of analog front end and digital signal processing blocks along with transducers. The basic block diagram of a DHA is shown in Figure 1.2. The incoming sound signal is captured by the microphone and is given to an analog to digital converter (ADC). The digital output from the ADC is processed by the digital signal processor (DSP) and the processed signal is converted back to analog using digital to analog converter (DAC) before sending it to the receiver.

Figure 1.2: DHA block diagram

<sup>&</sup>lt;sup>1</sup>source : http://www.hearinglink.org/

The microphones for hearing aids need to have low power consumption, small size and low sensitivity to vibration. A uniform frequency response over a range of 200 Hz to 5 kHz is desirable. A microphone with high sensitivity and low equivalent input noise (EIN) level has to be chosen while designing a hearing aid system. An electret condenser microphone (ECM) is most widely used in hearing aids. The MEMS microphones have started replacing ECM because of its lower power consumption, smaller size and uniform response over a wide frequency range.

Receivers also have to be small in size and free from vibrations. Advanced techniques like balanced armature technology improved the vibration performance of hearing aid receivers. The maximum output SPL of hearing aids largely depends on the capability of the receiver. The selection of receivers also depends on the hearing aid type since different styles require different size and output power.

An audio CODEC (Coder-Decoder) is composed of ADC and DAC. A CODEC can either be integrated into DSP or be used as a standalone chip. Low power consumption, small size, high dynamic range and high resolution are the main requirements of a CODEC for hearing aid application.

There is an acoustic feedback path from the receiver to the microphone. The microphone picks up the receiver output sound and causes a whistling or other audible artifacts. The presence of acoustic feedback limits the maximum gain that can be applied to a hearing aid. The effect of feedback largely depends on the type of hearing aid and the physical structure. It will be high in the case of a CIC with a vent. The feedback problem will be minimum in the case of RIC since the receiver is well isolated from the microphone.

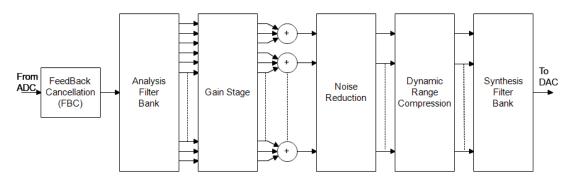

The fundamental concept of hearing aid is to amplify the signal level in a particular frequency range where there is hearing loss as per the audiogram. In a DHA, the digital signal processing block does this function. A basic hearing aid DSP block consists of feedback cancellation (FBC), filter bank (FB), noise reduction (NR) and dynamic range compression (DRC) algorithms. The block diagram of a hearing aid DSP is shown in Figure 1.3.

Since there is a need to modify the magnitude of the frequency response according to the audiogram, a filter bank algorithm is needed to adjust the gains at various frequencies individually. The Analysis filters split the entire incoming signal into smaller bands. The insertion gain obtained from the prescription formula is applied to each band and later, finetuning is done manually. After processing each band, a synthesis filter bank combines each band and gives the final output.

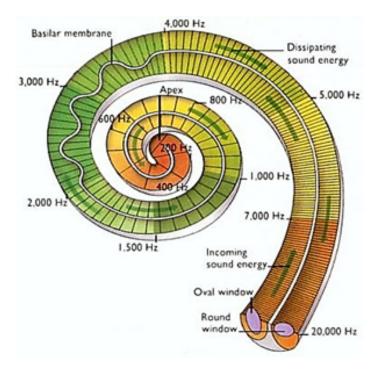

The frequency response of the cochlea is distributed in a non-uniform manner as shown

Figure 1.3: DSP block diagram

in Figure 1.4. So there are two different approaches to design filter banks for hearing aids: uniform and non-uniform. Uniform filter banks split the entire spectrum into bands of equal frequency resolution and are comparatively easy to design. In non-uniform filter banks, the auditory spectrum is divided into bands of different frequency resolutions and it gives better audiogram matching with a lesser number of bands. Hearing aid designers prefer finite impulse response (FIR) filters over infinite impulse response (IIR) filters as it provides linear phase, lower error and higher stability.

Figure 1.4: Frequency distribution inside cochlea<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>source: https://universe-review.ca/R10-16-ANS06.htm

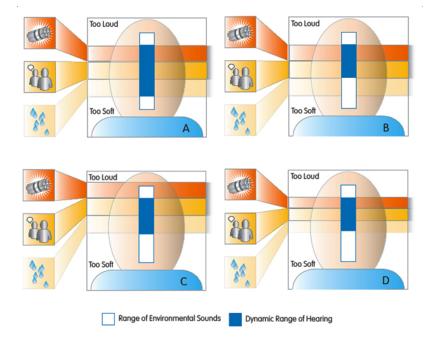

For hearing impaired people, generally the lower threshold of hearing increases while the upper threshold remains the same. This causes a reduction in the range of audible SPL compared to normal people. So hearing impaired people may feel increased growth of loudness when SPL increases from lower value to higher value. This phenomenon is commonly called as recruitment. Because of recruitment, there is a need for compressing the wider dynamic range of input signal SPL into the residual range of hearing impaired people. This is done through a dynamic range compressor (DRC) circuit. DRC can be either single channel or multichannel. As the number of channels increases, the circuit complexity also increases, which causes higher power consumption. In most of the hearing aid algorithms, after applying the insertion gain, bands will be combined into a smaller number of channels before applying DRC.

Noise reduction algorithm is used to preprocess the signal before applying to DRC. DRC will increase the amplitude of low intensity signals more, compared to high intensity signals, which may increase the effect of noise.

Feedback cancellation algorithms are adaptive in nature. In the basic feedback cancellation algorithm, the output is multiplied by a weighting factor and the result is then subtracted from the microphone signal producing a difference signal. A self- adjustment block continuously updates the weighting factor in response to the attenuation factor (Schaub (2008)). Generally, FBC is applied before splitting the signal into different bands.

In high-end hearing aids, more sophisticated algorithms like beamforming techniques for adaptive directionality, wireless protocols for communicating with mobile phones and remote controls, classification algorithms for automatically adapting to the changing environment, localisation algorithms for binaural hearing etc., may also be included.

## **1.2** Motivation and Research Objectives

A considerable portion of the world population is suffering from disabling hearing loss and they can benefit from hearing aids, cochlear implants and other assistive devices, sign language and other forms of educational and social support. The current production of hearing aids meets less than 10% of global need according to WHO. One major reason why people having hearing loss are not adopting hearing aids is its value for money. According to a survey by *The Hearing Review*, the average cost of a hearing aid per ear goes above \$2000 (Strom (2014)). So for a pair of hearing aids, the cost is not affordable for a person from a middle or low income group. Following conclusions are made from the literature survey on current state of the art hearing aids. The three primary challenges for a hearing aid IC design, i.e., low power, small size and high sound quality may not change in the near future (OnSemiconductor (2014)). The IC should work well with a supply voltage as low as 1 V and the overall current consumption has to be less than or around 1 mA. Qiao et al. (2011) suggested an area constraint of 25 mm<sup>2</sup>. Various studies suggest that delay has to be as small as possible. Bauml and Sorgel (2008) reported that even a 3 ms delay is noticeable and a 10 ms delay is significant. One major difficulty in analyzing various chip implementations is that most of the designs do not mention the delay performance of the systems in their results.

Considering the four basic signal processing algorithms required in hearing aids, FB and DRC perform the fundamental functions of loudness compensation and compression which are important, while FBC and NR are required for further signal enhancement and are optional. FBC largely depends on the final mechanical design of the hearing aid. So it is difficult to decide on the feedback cancellation algorithm to be included in the final design of the hearing aid without having a real-time measure of the actual feedback. Feedback cancellation algorithm can be avoided with a better physical design.

Most common fitting procedures NAL-NL1 and NAL-NL2 prescribe their gains in 1/3octave bands. Therefore, most of the recent research on filter banks concentrates on 18-band 1/3-octave structure to get a perfect fitting. But 18-band structure results in large delay especially in lower frequency bands. Uniform filter banks are the most common choice in the hearing aid industry. But the problem with uniform filter bank is that it requires large number of bands to get better resolution at lower frequencies. For example, in the case of the 18-band 1/3-octave filter bank, the lowest frequency resolution is as low as 40 Hz. To get that level of resolution with a uniform filter bank, at least 200 narrow band filters are needed which will involve a large number of computations.

In DRC algorithms, according to ANSI S3.22 specifications, the attack time and release time are defined in terms of the time taken by the output signal to reach within 3 dB and 4 dB of its final value respectively. All the currently available algorithms calculate the time constants in terms of input signal level and none of them consider the effect of gain stage on the time constants. These algorithms are originally derived from general audio processing applications, where slight variations in dynamic parameters may not make much difference in the final output since the people using those applications would be having normal hearing. But in the case of hearing impaired people a precise control over time constants is preferred, because even small variations in the time constants may affect the

speech quality and intelligibility (Schaub (2008)). Because of the two stage filtering, the smoothing algorithm also affects the effective time constants adversely.

Various surveys on customer satisfaction show that low speech quality is the main reason for people not wearing their hearing aids. Especially the difficulty in speech recognition in highly non-stationary environment is still the number one problem associated with hearing aids. So there is a need for a better noise reduction algorithm which can be used for realtime processing with minimum delay and limited power consumption.

All these emphasise that there is a requirement for a high user value hearing aid affordable for middle and low income group in developing countries. Studies on current state of the art techniques suggest a need for further optimisation in the area of filter bank and dynamic range compression algorithms. Based on these factors, the following objectives have been formulated for this research work.

1) To develop a digital filter bank and dynamic range compression algorithms with low power consumption and acceptable delay for a hearing aid application, which can be programmed by any of the available nonlinear prescriptive formulas.

2) Hardware design and implementation of the developed algorithms to fabricate as a signal processing ASIC and real-time testing of the design using FPGA.

### **1.3 Design Approach**

### i) Objective 1:

FIR filters offer better stability and linear phase compared to IIR filters. Even though there is not much significance for phase response in the context of speech intelligibility, linear phase is important if any feedback cancellation algorithm needs to be included. It also helps in maintaining binaural cues which are required for acoustic directionality. So an FIR filter approach was adopted in designing the filter bank. Uniform and non-uniform FB techniques have their own advantages and disadvantages as discussed earlier. Even though uniform filter banks are predominantly used compared to non-uniform structures in practical circuits, a lot of research has been carried out in non-uniform domain in the last decade. Most of the recent research focus on the 18-band ANSI S1.11 structure to get perfect audiogram matching. Because of its high computational complexity and delay, these algorithms are yet to be considered as a practical choice in hearing aids. However, there is scope for further optimisation for the currently available architectures. Thus a non-uniform approach that satisfies the ANSI S1.11 specifications and having a reduced computational

complexity and acceptable delay performance is adopted in this work. The feasibility of the proposed design was proved by implementing the entire filter bank architecture using semicustom design flow and analyzing the frequency matching error performance and power consumption.

Dynamic Range Compression algorithms contain two fundamental blocks: level detection and gain stage. In traditional algorithms, a single-pole low pass recursive filter has been used for level detection. The effect of the gain stage on the estimation of the time constants was studied and an algorithm which gives accurate attack and release time values as defined in ANSI S3.22 standard for hearing aid specifications was developed. A smoothing stage can be included in DRC to reduce the distortion due to word length errors. In that case, adverse effects on time constants due to two-stage filtering was eliminated by proposing new methods to estimate the decay coefficients.

### ii) Objective 2:

Being a real-time device which works on low voltage and limited capacity batteries, verifying the performance of the hardware implementation of the algorithms intended for hearing aids is crucial. Hardware implementation of the proposed algorithms was carried out using standard register transfer level (RTL) techniques using Verilog Hardware Description Language (HDL). Industry-standard electronic design automation (EDA) tools are used for the design and analysis of the design at every stage. The functionality of the algorithms was verified using a software platform before doing the hardware design. To get a fair idea about the performance of the design, a technology node of 65 nm from United Microelectronics Corporation (UMC) that provides 1.2 V low power design libraries was used, which matches the battery voltage of the hearing aid. Texas Instruments has an ultra-low power audio CODEC (AIC111) designed for hearing aids. We plan to use this CODEC as the analog front end to be interfaced with our proposed ASIC. The CODEC is provided with a master SPI protocol to communicate with interfacing devices. So an SPI slave protocol is required, which is compatible with the CODEC protocol. Two Digilent ZedBoards having ZynQ-7000 FPGAs from Xilinx<sup>®</sup> were used for testing the functionality of the hardware design in real-time. The design was ported to SCL 180 nm technology also by properly following the vendor specific EDA tool flow for each stage with an intention to fabricate the chip.

## **1.4** Contribution of the Thesis

A digital signal processing ASIC intended to work as a processing module inside a digital hearing aid is presented in this thesis. In the proposed ASIC, modified filter bank and dynamic range compression algorithms are included, and the functionality was tested and verified in real-time using FPGA. Along with the design details about the proposed ASIC, a detailed explanation of various features, fitting procedure, and the current research trends in state of the art hearing aids are also included. The disadvantages of current hearing aids were studied and the design requirements were decided based on the literature survey given in chapter 2.

Current dynamic range compression algorithms estimate the decay coefficients erroneously. A new formula relating attack and release time parameters, envelope tracking decay coefficients and compression ratio parameters is proposed for the dynamic range compression algorithm for hearing aid application. An absolute detector based and an RMS detector based feed-forward architectures with and without smoothing stages were implemented using 4-bit and 8-bit resolution LUT based logarithm at hardware level using UMC 65 nm standard cell libraries. The approximation errors and the post-layout core power consumption analysis show that the proposed techniques give accurate expected output at required time instants while conventional methods give erroneous output values. There is no significant difference in power consumption with an increase in log table resolution, while the approximation error reduces significantly. Smoothing stages can be included if a continuous gain transition is needed with the cost of increased power consumption. These results suggest the use of an absolute level detector based DRC without the smoothing stage for lowest power consumption and overall performance, using modified decay coefficient estimation techniques for a low power hearing aid design. In applications where high quality of sound is important, a smoothing filter can be incorporated at the output stage.

A complexity-oriented architecture for ANSI S1.11 1/3 octave Class-2 filter bank for hearing aids is also proposed as part of this work. A method to define band edge frequencies of each prototype filter to get minimum orders that satisfy the required specifications is developed. Hardware implementation of the algorithm was carried out using 65 nm standard cell libraries and the output was tested with NAL-NL2 prescription for different audiograms. The maximum matching error was within the practical limit of  $\pm 1.5 \, dB$ . The proposed architecture shows more than 50% reduction in the total number of filter coefficients required compared to other ANSI S1.11 based designs and less than 10 ms group delay with practically feasible power consumption. A complete hardware implementation and the audiogram matching results for the designed hardware of the proposed 18-band ANSI S1.11 filter bank is one of the major highlights of this thesis. Similar implementation results for an ANSI S1.11 based filter bank is not reported previously to the best of our knowledge.

Fabricating the whole chip with the proposed architectures using 65 nm technology is not viable because of the high cost for fabrication. So an ASIC with the proposed filter bank combined with the DRC architecture was implemented using 180 nm standard cell library with an intention to fabricate from the facility available at Semi-Conductor Laboratory, Chandigarh, India (SCL (2020)). Even though the area and power consumption of the chip in 180 nm technology would be higher, a working prototype will add value to the research work and it can be used in a body worn type hearing aid if all the specifications are met as per the design. The chip was designed in such a way that it is programmable externally through the serial communication protocol. The functionality of the design was tested in real-time using two FPGAs, one of them modeled as the hearing aid chip and the other as an external audio CODEC. As a whole, this research work explains the design and implementation of a programmable digital hearing aid ASIC with modifications proposed to the currently available hearing aid algorithms.

### **1.5** Organisation of the Thesis

Chapter 2 explains the necessary background required to understand the functionality and general features of the hearing aids. The chapter also contains a detailed literature survey on various hearing aid implementations and their characteristics, filter bank structures and dynamic range compression algorithms.

The development and implementation of the dynamic range compression algorithm are explained in chapter 3. This chapter presents two different aspects of DRC inter-related to each other. In the first part, the conventional DRC algorithm and the proposed techniques to overcome the flaws of the conventional methods are given. In the second part, implementation details and hardware-level comparison of eight different DRC architectures are described and conclusions are made based on the simulation results of different architectures to chose the appropriate design according to the specific hearing aid requirement.

The 18-band ANSI S1.11 filter bank design is described in chapter 4. The theoretical explanation of the algorithm as well as finer details of the hardware architecture are given in this chapter. It is concluded with the analysis of hardware implementation results and

audiogram matching error performance of the proposed design corresponding to different hearing losses.

The details of the implementation of proposed hearing aid ASIC using SCL-180 nm technology is given in chapter 5. The real-time testing of the proposed hearing aid algorithm using FPGAs and the design of the SPI slave protocol are also included in this chapter. Finally, the summary of the research work is given in chapter 6. This chapter also contains the scope for future research in the field of digital hearing aid, more specific to the topics covered in this thesis.

# Chapter 2

# **Review of Digital Hearing Aids**

A digital hearing aid is a complex real-time system capable of performing audio signal enhancement according to the requirements of a particular hearing loss. Every hearing aid is equipped with a wide range of features, even though the power and delay constraints are stringent. A general overview of current hearing aids is given in the first part of this chapter. Various aspects such as types of hearing loss, types of hearing aids, the way hearing aids get fitted and the common terms related to hearing aids and hearing aid research are addressed. In the second part, a detailed literature survey on hearing aids is given. It starts with a review on user satisfaction and problems with the current state of the art hearing aids followed by a survey on various hearing aid implementations and its features. Further, various filter bank algorithms and dynamic range compression algorithms available for hearing aids are explored.

## 2.1 Types of Hearing Loss

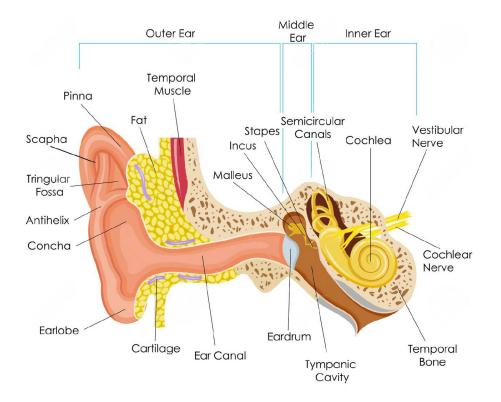

Hearing loss can be categorised into three types based on which part of the auditory process is affected. A cross-section of the human ear is shown in Figure 2.1.

#### i) Conductive hearing loss:

Conductive hearing loss happens due to the problems with the ear canal, eardrum or middle ear and its little bones. It results in a reduction in sound intensity, reaching the inner ear. So a conductive hearing loss can be mitigated by increasing the sound intensity according to the air-bone gap information that can be obtained from the audiogram. Hearing aids work well for compensating the conductive hearing loss.

Figure 2.1: Cross-section of human ear<sup>1</sup>

### ii) Sensorineural hearing loss (SNHL):

When hearing loss is due to the problems of the inner ear (cochlea and auditory nerve), it is called sensorineural hearing loss. The major reason for SNHL is the loss of hair cell functionality inside the cochlea. Any kind of damage to the hearing nerves also results in SNHL. It is an irreversible or permanent condition. Along with the reduction in sound intensity, it also causes distortion in perceived speech signals. Hearing aids can be used to assist people with sensorineural hearing loss by enhancing the frequencies corresponding to damaged hair cells.

### iii) Mixed hearing loss:

Mixed hearing loss refers to the hearing loss due to the combination of conductive and sensorineural losses.

<sup>&</sup>lt;sup>1</sup>source: http://www.123rf.com

### 2.2 Types of Hearing Aids

Based on the style, size and where it is worn, currently available hearing aids can be categorised into any of the following types.

#### i) Body worn hearing aids:

Body worn is the oldest version of hearing aids. It consists of a processing module and a receiver, which is connected to the module by a cable. Signal acquisition and processing take place in the module and the processed sound is played through the receiver. These hearing aids can provide large amplification. Poor sound quality due to ineffective sound acquisition is the major disadvantage. Since the processing element is separated from the receiver and has to be carried in a pocket, maintenance is a problem. Lower cost and higher battery capacity still help it to continue in the market.

#### ii) Behind The Ear (BTE):

Behind the ear hearing aids consist of a case, an earmold or dome and a connection between them. The case contains the electronics, controls, battery, microphone(s) and often the loudspeaker. Generally, the case sits behind the pinna with the connection from the case coming down the front into the ear. BTEs can be used for mild to profound hearing loss. Comparatively lower price, flexibility to use for a larger range of hearing loss and easy maintenance make it the most common style among hearing aids. Larger size compared to other types besides body worn is a disadvantage.

#### iii) Receiver In Canal (RIC):

Unlike BTEs, the receiver in a RIC device is housed entirely inside the ear. RICs are smaller devices worn behind the ear with a small wire running down into the ear canal attached to the receiver. Some of the advantages with this approach include improved sound quality, reduced case size, immediate patient fitting and the possibility of open-fit technology without having much feed-back problem. Small batteries with lesser capacity, higher cost and difficulty in maintenance are the major disadvantages.

#### iv) In The Ear (ITE):

In the ear devices fit in the outer ear bowl (called the concha). They are sometimes visible when standing face to face with someone. ITE hearing aids are custom made to fit

each individual's ear. They can be used in mild to severe hearing losses. Feed-back can be a problem in case of severe hearing loss. Earwax and moisture can easily build up and affect performance.

### v) Completely In Canal (CIC)

Completely in canal aids are generally not visible unless the viewer looks directly into the wearer's ear. These aids are intended for mild to moderately severe losses. CICs are usually not recommended for people with good low-frequency hearing, as the occlusion effect is much more noticeable. Venting makes acoustic feed-back a severe problem in CIC devices.

### vi) Invisible In Canal (IIC):

Invisible in canal hearing aids fit inside the ear canal completely, without leaving any visible trace of hearing aid externally. Extended wear hearing aids are hearing devices that are non-surgically placed in the ear canal by an ENT surgeon. These devices are worn for 1–3 months at a time without removal. They can be used by people with mild to moderately severe hearing loss. Higher cost, difficulty in handling and lack of flexibility are some of the disadvantages of IIC type. Different types of hearing aids are shown in Figure 2.2.

Figure 2.2: Types of hearing aids<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>source: http://www.rsfaudiology.com, http://www.medicalexpo.com/prod/phonak/product-78004-512410.html, https://www.bestsoundtechnology.com/

### 2.3 Hearing Aid Fitting Procedure

A patient having hearing loss has to go through a few steps before starting to use a hearing aid. An audiologist, who is a specialist in treating hearing loss will measure the degree of patient's hearing loss and decide the best possible solution after going through a set of standard procedures as explained below:

#### i) Hearing Test:

The first step in fitting a hearing aid is to understand the severity of the loss. A hearing test will be carried out in a soundproof room with a calibrated audiometer, which can produce sounds at different frequencies at specified levels. The audiologist plays these sounds at very low intensities through a calibrated headphone. Then the intensity level is gradually increased until the sound becomes audible. The softest sounds heard by the subject at each frequency are recorded as the thresholds. Most hearing tests analyse sounds between 125 Hz and 8 kHz and from -10 dB to 120 dB SPL. From these recorded data, SPL v/s frequency graph is plotted. The hearing test will be conducted in both the ears. An 'X' mark in the audiogram indicates the left ear and 'O' the right ear. The test using a headset is called as air conduction test. When air conduction shows a loss, a bone conduction test will be carried out to identify the conductive hearing loss. A small bone conduction vibrator will be placed on the mastoid bone directly behind the ear and sound is transmitted through the bones of the skull to the inner ear, bypassing the outer and middle ear. The audiogram will be plotted in the same way as in the air conduction test. A difference between air and bone conduction thresholds indicates a loss due to problems with the outer or middle ear, i.e., a conductive loss.

#### ii) Audiogram Matching:

Based on the audiogram and the patient's choice, the audiologist chooses a particular hearing aid. A hearing aid fitting software will be provided by every manufacturer, which contains all configurable options available for the particular hearing aid. One of the most important parts of the entire flow is the initial fitting. Various prescription formulas are available which give gain curves according to the audiogram. Most common methods available for hearing aid gain prescription are: NAL-RP (National Acoustic Laboratory-Revised Profound), NAL-NL1(Non-Linear 1), NAL-NL2(Non-Linear 2), DSL I/O(Desired Sensation Level Input/Output), IHAFF(Independent Hearing Aid Fitting Forum), FIG-6 and POGO-II. Hearing aid manufacturers may have their own fitting formulas as well. Still, most of them use the NAL series and DSL for initial fitting (Johnson (2012)). After the initial fitting, fine-tuning is done by adjusting the gain in each band manually, considering patient feed-back.

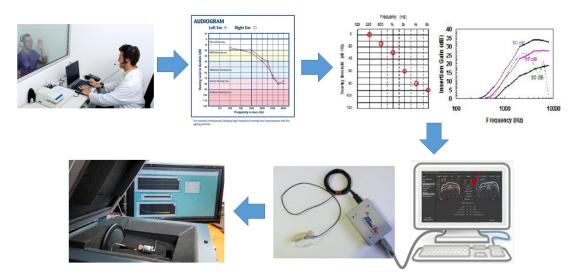

### iii) Programming the hearing aid and testing the output:

After the initial fitting, the parameters will be loaded into the hearing aid using any of the hearing aid programming interfaces. The most common ones are Hi-Pro and NOAHlink. After loading the parameters into the hearing aid, it will be tested using a 2cc coupler by inserting inside a testing equipment. The parameters like delay, attack time, release time, frequency range, THD, OSPL90 etc., can be obtained from this test. Minimum performance requirements for a hearing aid according to WHO guidelines for designing hearing aids for developing countries is given in Table 2.1 (WHO (2004)). The entire hearing aid fitting procedure flow is shown in Figure 2.3.

| Maximum OSPL <sub>90</sub>     | 118 dB (± 4 dB)                                        |

|--------------------------------|--------------------------------------------------------|

| OSPL <sub>90</sub> at 1 kHz    | 114 dB (± 4 dB)                                        |

| Maximum full-on acoustic gain  | 45-55 dB (+5/0 dB)                                     |

| Full-on acoustic gain at 1 kHz | 42 dB (+5/0 dB)                                        |

|                                | 200 Hz to 4500 Hz                                      |

|                                | $(200 \text{ Hz to } 2000 \text{Hz} \pm 4 \text{ dB},$ |

| Basic frequency response       | 2000 Hz to 4000 Hz $\pm 6dB$ ,                         |

|                                | on nominal frequency                                   |

|                                | response curve                                         |

| Total harmonic distortion      | 500 Hz < 5%                                            |

|                                | 800 Hz < 5%                                            |

| at 70 dB SPL input             | 1600 Hz < 2%                                           |

| Equivalent input noise level   | < 25 dB SPL                                            |

| Battery current                | $\leq 1 \text{ mA}$                                    |

Table 2.1: Minimum performance requirements of a hearing aid (WHO (2004))

Figure 2.3: Hearing aid fitting procedure<sup>3</sup>

### 2.4 Hearing Aid Characteristics and Definitions

Definitions of some of the important terms related to digital hearing aids are given below (ANSI (2003) and Invensense (2003)):

Sound Pressure Level (SPL):

Sound pressure level is a measure of RMS value of sound expressed in decibels relative to a reference level of 20  $\mu$ Pa.

Output SPL for 90 dB input SPL (OSPL90):

OSPL90 is defined as the SPL developed at the output when the input SPL is 90 dB when the gain control of the hearing aid is full-on, i.e., when the volume control is set to maximum.

Full-on Acoustic Gain:

It is the result obtained at each test frequency by subtracting the input SPL from the SPL at the output of the hearing aid with the gain control set to its full-on position with an input SPL of 50 dB.

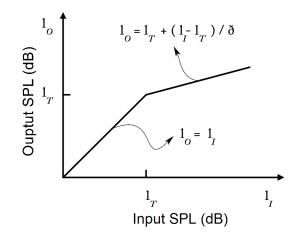

Compression Ratio (CR):

Compression ratio is the ratio of change in input SPL to change in output SPL in a compression curve.

<sup>&</sup>lt;sup>3</sup>source: http://helpingmehear.com/, http://www.hearingessentials.com, http://www.audiologyonline.com, http://www.centuryhearingaids.com, http://sine.ni.com/cs/app/doc/p/id/cs-15033

#### Attack Time (AT):

Attack time is defined as the time between the abrupt increase from 55 to 90 dB and the point where the level has stabilised within 3 dB of the steady-state value for the 90 dB input SPL.

#### Release Time (RT):

Release time is defined as the interval between the abrupt drop from 90 to 55 dB and the point where the signal has stabilised to within 4 dB of the steady state value for the 55 dB input SPL

#### Compression Factor (CF):

Compression factor is the inverse of compression ratio, i.e., the ratio of change in output SPL to change in input SPL in a compression curve.

#### Compression Threshold (CT):

Compression threshold is the point at which the gain changes in a dynamic range compressor.

#### Sensitivity of a microphone:

The sensitivity of a microphone is defined as the electrical response at its output to a given standard input of 1 kHz sinewave at 94 dB SPL, or 1 pascal. A microphone with a higher sensitivity value has a higher level output for a fixed acoustic input.

#### Equivalent Input Noise (EIN) of a microphone:

Equivalent input noise is the output noise level of the microphone expressed in dB SPL, as a theoretical external noise source placed at the microphone's input. Input SPLs below the EIN level are under the noise floor of the microphone and outside the dynamic range of signals for which the microphone produces an output.

## 2.5 User Satisfaction and Problems with Current Hearing Aids

If a patient fitted with hearing aid feels that there is no advantage in wearing a hearing aid or if it causes any other adverse side effects, the person may stop using it. It is necessary to understand and solve the major reasons why patients stop using hearing aids. There are few studies available in the literature on why people are not using hearing aids even after spending a large amount of money and time to buy and get it fitted by an audiologist. Understanding these factors may help hearing aid designers to come up with better solutions. In one of the most comprehensive studies by McCormack and Fortnum (2013), the authors have collected most of the available data on user satisfaction via a scoping study. Out of those, they have selected 10 articles reporting reasons for non-use of hearing aids and found a number of reasons including hearing aid value, fit and comfort, maintenance of the hearing aid, attitude, device factors, financial reasons, psychosocial/situational factors, healthcare professionals' attitudes, ear problems and appearance. In almost all the articles, the most important issue was the hearing aid value, i.e., the hearing aid did not provide enough benefit and comfort to the hearing impaired. Most of the people chose lack of speech clarity as the main cause of discomfort. Another important conclusion was, the stigma of wearing hearing aids had minimal impact on discontinuation.

Puder (2009), in an article on state of the art, challenges and future trends in hearing aids, claimed, reduced speech intelligibility in noisy environments as the top-ranked problem of hearing aid users and may continue as the major problem in future hearing aids too. Eric Healy, (Edwards (2015)), also noted that the difficulty of understanding speech in background noise as the number one complaint of people using a hearing aid and considered it as the "Holy Grail" in the case of hearing aid design. There are many surveys on the effectiveness of various noise reduction algorithms present in hearing aids as well. Chong and Jenstad (2018) have published one of such studies, in which the authors have comprehended the results of different single microphone noise reduction studies. In hearing aids, adding a highly advanced noise reduction algorithm is not feasible due to its power constraint and real-time requirement. According to the study, advanced noise reduction algorithms are yet to be tested on hearing aids. The paper concludes that current noise reduction algorithms are not useful for improving speech intelligibility, but may help in terms of improving listening comfort and release of cognitive load for a secondary task (i.e., dual task paradigm, such as evaluating the listening effort when a secondary visual task is carried out).

There are studies on the effectiveness of hearing aids between different languages like English and Mandarin. In one such recent studies (Wong et al. (2018)), the authors suggest that different signal enhancing algorithms may work differently on different languages. Mandarin is more vowel centric than consonant centric. So low frequency is more important for speech understanding than English. English on the other hand, is more consonant centric. So the algorithms, especially like noise reduction, work differently for tonal languages. But in some studies as by (Ho et al. (2013)), the objective parameters such as Acceptable Noise Level (ANL) are similar for Mandarin and English. So in such studies, there is no significant difference in the effectiveness of algorithms on different languages. As of now, we could not find any such studies based on Indian languages, which are phonetic in nature. A proper study on the effectiveness of the different hearing aid algorithms for Indian languages may be helpful in developing better algorithms for hearing aids specific to Indian conditions.

There are some classic studies from earlier days using multiple hearing aids of different manufacturers (Alcántara et al. (2003), Bentler and Chiou (2006), Sarampalis et al. (2009)) on the effectiveness of hearing aids. According to Alcántara et al. (2003), the most commonly reported difficulty of people with even a mild sensorineural hearing loss is reduced speech intelligibility in environments where there is background noise or competing speech, and the hearing aids in most cases, instead of alleviating this problem, actually increases it. Even though the noise reduction algorithms may increase the apparent Signal to Noise Ratio (SNR), there is rarely any improvement in speech intelligibility.

Overall, various studies on user satisfaction and problems with current hearing aids clearly show that the majority of hearing aid wearers are not satisfied with the speech clarity, especially in disturbing noisy background conditions. Even though the presence of noise reduction algorithms improves the ease of hearing, or reduces the hearing effort, there is no proper improvement in overall speech intelligibility. Speech quality being the primary requirement for hearing aid wearers, the research should focus on improving the quality of algorithms present in hearing aids. Considering the fact that advanced and complicated algorithms are not yet tested on hearing aids due to its design constraints and showing some dependency on certain language characteristics, developing noise reduction algorithms for hearing aids is also a good and interesting area of research.

## 2.6 Hearing Aid Chip (HAC) Implementations

A hearing aid can be considered as one of the most challenging applications when it comes to IC design because of its real-time processing and stringent low power requirement. For hearing aid designers, there can be three primary challenges (OnSemiconductor (2014)): high performance (in terms of sound quality and computational capability), low power consumption (a battery current drain  $\leq 1$  mA) with limited supply voltage (approximately 1 V) and small physical size (depending on the style). Since all three are interrelated, it is the task of the designer to find a trade-off between these challenges. There are different options in the case of hardware platforms available for the researchers to implement the signal processing algorithms for hearing aids. For testing the algorithm in real-time during the initial stages of the design, it is a common practice to use low power general-purpose digital signal processors. Because of its size and comparatively higher power consumption, it is difficult to consider these processors for hearing aid products other than body worn type. Field Programmable Gate Arrays (FPGAs) are another option available for testing the algorithms in real-time. Application Specific Integrated Circuits (ASICs) with custom-designed dedicated architectures for the particular signal processing techniques are the best way to realise the algorithms in hardware.